# Simulation Framework and Thorough Analysis of the Impact of Barrier Lowering on the Current in SB-MOSFETs

Mike Schwarz, Laurie E. Calvet, John P. Snyder, Tillmann Krauss, Udo Schwalke, and Alexander Kloes

Abstract—In this paper we present a simulation framework to account for the Schottky barrier lowering models in SB-MOSFETs within the Synopsys TCAD Sentaurus tool-chain. The improved Schottky barrier lowering model for field emission is considered. A strategy to extract the different current components and thus accurately predict the on- and off-current regions are adressed. Detailed investigations of these components are presented along with an improved Schottky barrier lowering model for field emission. Finally, a comparison for the transfer characteristics is shown for simulation and experimental data.

Index Terms—2D Poisson equation, device modeling, Double-Gate (DG) MOSFET, field emission, framework, Schottky barrier, Synopsys, TCAD, thermionic emission, thermionic and tunneling current

### I. Introduction

THE semiconductor industry is today dominated by device structures such as Intel's tri-gate [1], and fully-depleted SOI devices [2]. These multi-gate devices enhance electrostatics and address short-channel effects (SCEs) and device performance degradation.

However, there remain some important issues that still need to be considered. One of these technological limits that continues to present an important obstacle is the increased impact of source/drain (S/D) parasitic resistances [3]. One solution is to consider changes in device technology and in particular the device structure.

In this context the Schottky barrier (SB) MOSFET is a very promising candidate to enhance transistor performance due to its metallic S/D electrodes with low specific resistances and high scalability even down to the sub-10nm region. Its good process compatibility with standard CMOS technologies makes this concept even more attractive.

Schottky barrier MOSFETs offer additional advantages such as reduced substrate leakage and performance enhancements at low temperature due to the presence of the Schottky barrier.

- M. Schwarz is with Robert Bosch GmbH, Germany (e-mail: mike.schwarz1980@googlemail.com).

- L.E. Calvet is with Université Paris-Sud, France.

- J.P. Snyder is with JCap, LLC, USA.

- T. Krauss and U. Schwalke are with Technische Universität Darmstadt, Germany.

- A. Kloes is with Technische Hochschule Mittelhessen, Germany.

These lead to less channel doping, typically used to control the off-state leakage currents, and thus improved mobility as well as reduced junction and gate capacitances. This in turn results in substantial power and speed performance improvements [4], [5].

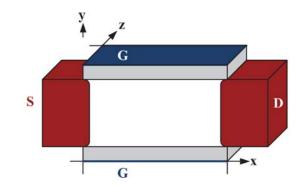

Fig. 1. Simplified geometry of a SB-DG-MOSFET. S/D are metal contacts for the SB-DG-MOSFET.

An important effect in Schottky barrier devices is the imageforce induced lowering of the barrier, also known as the Schottky barrier lowering (SBL) effect [6]. It has an enormous impact on device performance. Calvet [7] showed that field emission characteristics will become more important at lower temperatures and in [8] demonstrated the low leakage behavior of low doped SB-MOSFETs. R. Vega showed that the SBL in Si SB-MOSFETs can enhance the device performance at room temperature [9], but concentrated on the impact of thermionic emission. Padilla et al. used in [10] an external approach to include a SBL estimation quasi fully self-consistently using the Silvaco Atlas [11] tool-chain, for both thermionic and field emission as discussed in R. Vega's paper in [12]. Schwarz et al. applied in [13] an improved SBL model offered by Synopsys TCAD Sentaurus [14] and analyzed the physical behavior of group IV and III-V Schottky Barrier MOSFETs at cryogenic temperatures.

In the past, various numerical studies of Schottky barrier Multi-Gate MOSFETs have been published based on device simulators like Synopsys TCAD Sentaurus [14].

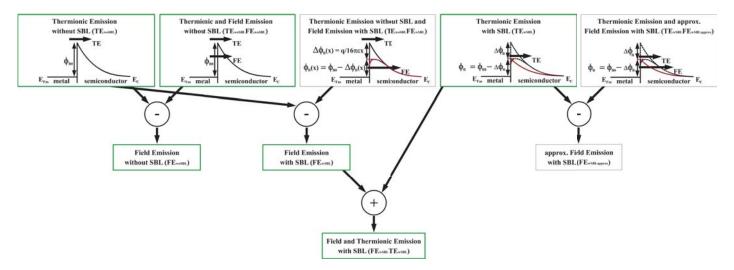

Fig. 2. Schottky barrier current component extraction in the Synopsys TCAD Environment. The highlighted current components are used for further analysis.

In this paper a framework is presented for the Synopsys TCAD tool-chain to account for a more precise estimation of the Schottky barrier lowering effect using the different SBL models as applied in [13]. The current components from the various SBL models are extracted for the structure shown in Figure 1. To the best of our knowledge, a framework as presented below including full self-consistent TCAD simulations is done for the first time.

## II. BOUNDARY CONDITIONS OF SCHOTTKY CONTACTS

Within the Sentaurus Device simulator of the Synopsys TCAD tool-chain Schottky contacts are defined with the following boundaries (further details available in [6], [15], [16])

$$\phi = \phi_{\rm F} - \phi_{\rm B} + \frac{kT}{q} \ln \left( \frac{N_{\rm C}}{n_{\rm i,eff}} \right) \tag{1}$$

$$\vec{J}_{n} \cdot \hat{n} = qv_{n} \left( n - n_{0}^{B} \right)$$

$$\vec{J}_{p} \cdot \hat{n} = -qv_{p} \left( p - p_{0}^{B} \right)$$

(2)

$$n_0^{\rm B} = N_{\rm C} \exp\left(\frac{-q\phi_{\rm B}}{kT}\right)$$

$$p_0^{\rm B} = N_{\rm V} \exp\left(\frac{-E_{\rm G,eff} + q\phi_{\rm B}}{kT}\right)$$

(3)

where  $\phi_F$  is the Fermi potential at the contact,  $\phi_B$  is the barrier height, k is the Boltzmann constant, T is the temperature,  $N_C$  is the density-of-states at the conduction band,  $n_i$  is the intrinsic carrier concentration,  $\vec{J}_n$  is the electron current density,  $\vec{J}_p$  is the hole current density,  $v_n$  and  $v_p$  are the thermionic emission velocities,  $n_0^B$  and  $p_0^B$  are the equilibrium densities,  $N_V$  is the density-of-states at the valence band, and  $E_G$  is the band gap.

The contacts in the MOSFET, i.e. the source and drain Schottky contacts with  $\phi_{\rm B}=0.3{\rm eV}$  relative to the conduction band edge and the gate contact are defined in the Sentaurus

Device simulator of the Synopsys TCAD tool-chain by the following code:

```

Electrode

{

{ Name="source" Voltage = 0.0 Schottky Barrier = 0.3 }

{ Name="drain" Voltage = 0.0 Schottky Barrier = 0.3 }

{ Name="gate" Voltage = 0.0 }

}

```

### III. THERMIONIC AND TUNNELING CURRENT IN TCAD

The currents in the Synopsys TCAD environment are treated by the boundary condition given above in (2). For simplification the general expressions for the thermionic and field emission are given. For detailed equations within the Synopsys TCAD tool refer to [14].

The thermionic emission (TE) according to Bethe [17] can be expressed as

$$J_{TE} = A_{n,p}^{**} T^2 \exp\left(-\frac{q\phi_B - q\Delta\phi}{kT}\right) \left[\exp\left(\frac{qV_{ds}}{kT}\right) - 1\right]_{(4)}$$

where  $A_{n,p}^{**}$  represents the effective Richardson constant,  $\phi_B$  the barrier to surmount (barrier + band bending),  $\Delta\phi$  the Schottky barrier lowering, and  $V_{ds}$  the applied drain-to-source voltage [6].

The field emission (FE) (tunneling current) is obtained by the transport model of Schenk and Heiser [18] and is a nonlocal process within the grid of the Synopsys TCAD simulation environment [14]. The field emission is converted into a local process as described in [19].

$$J_{FE} = \frac{qmkT}{2\pi^2\hbar^3} \int_{q\phi_{Bp}}^{q\phi_{Bn}} dE \cdot T(E) \cdot \ln \left[ \frac{1 + \exp(E - E_{Fs})/kT}{1 + \exp(E - E_{Fm})/kT} \right]$$

(5)

with q the elementary charge, m the effective mass, k the Boltzmann constant, T the temperature,  $\hbar$  the reduced Planck

constant, T(E) the tunneling probability, E the corresponding energy, and  $E_{\rm Fs}$  and  $E_{\rm Fm}$  the Fermi energies in the semiconductor and metal, respectively.

The field emission depends on the band edge profile along the entire path between the points connected by tunneling. This makes field emission (tunneling) a nonlocal process. In general, the band edge profile has a complicated shape, and must be computed by solving the transport equations and the Poisson equation. Additionally, T(E) the tunneling probability in (5) is calculated using the WKB approximation approach of [14], [20], [21], [22]. This is an accepted approximation of the tunneling probability where its overestimation is calibrated in real devices by fitting the effective mass.

An important effect in Schottky barrier devices is the imageforce induced lowering of the barrier energy, also known as the Schottky barrier lowering effect [6]. For reverse biased Schottky barrier devices it is obvious that the effective barrier has to be smaller than an unbiased Schottky barrier height and therefore higher currents are expected. Schottky barrier lowering has to be accounted for when computing T(E) in (5) and in (4) as well.

It follows for the Schottky barrier height:

$$\phi_{\rm B} = \phi_{\rm B0} - \Delta \phi_{\rm B}. \tag{6}$$

The final value of the Schottky barrier  $\phi_B$  is computed for electrons in the conduction band and for holes in the valence band. Schottky barrier lowering also influences the equilibrium concentration of electrons and holes corresponding to (3).

### IV. SCHOTTKY BARRIER LOWERING MODELS IN TCAD

Within the Sentaurus Device simulator there are different models to account for the Schottky barrier lowering effect for field and thermionic emission. One has to be careful to account for them correctly, otherwise overestimations can occur.

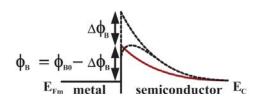

# A. Barrier Lowering for Thermionic Emission

The general Schottky barrier lowering model (neglecting dipole lowering) in the Sentaurus Device simulator is given by the well known Schottky barrier lowering model shown in equation (7). It takes into account the peak of the image-force profile (drawn in Figure 3 as the lower dashed line) and models the barrier with a simple reduction in height of the original profile (red profile of Figure 3) [6]. Applying the model for Sentaurus Device with appropriate choice of parameters will lead to the simplified equation as follows:

$$\Delta \phi_{\rm B} = \sqrt{\frac{q|E|}{4\pi\epsilon}} \tag{7}$$

with  $\left| E \right|$  is the absolute value of the electric field at the metal-semiconductor interface.

This model is reasonably accurate for thermionic emission, because to first order it depends only, as in (4), on the barrier

height that charge carriers have to surmount. Note however, that the effective channel length in this simplified model is larger than in the true SBL lowering, an effect that becomes more important as channel lengths are made smaller. The model can also be used to calculate the field emission components, however it tends to overestimate the current because the area of the barrier (red line of Figure 3) is significantly reduced in this simplified model compare to the more accurate barrier profile (lower dashed line of Figure 3).

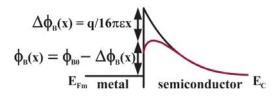

## B. Barrier Lowering for Field Emission

With the release of M-2016.12 Synopsys offers an additional SBL model for field emission that takes the image charge into account. The image charge barrier lowering model is nonlocal/position-dependent and corrects the band edge profile used in the WKB integral calculation along nonlocal lines (red line of Figure 4). It is given by

$$\Delta\phi_{\rm B}(x) = \frac{\rm q}{16\pi\epsilon x} \tag{8}$$

for an electron located at a distance x from the metal.

Field emission currents are predicted with more accuracy using this model as it considers a more realistic barrier profile (red line of Figure 4) compared to the simpler barrier lowering model discussed previously (red line of Figure 3). This model can only be applied to calculation of field emission currents. Thermal emission currents can only be calculated with the simpler model of equation (7) or, of course, with no barrier lowering model.

When this model is applied to field emission currents, calculation of thermal emission currents must be specified without any barrier lowering model at all in order to avoid conflicts between the two models. This is in contrast to the simpler barrier lowering model discussed above (equation (7)), which can be applied to both field and thermal emission currents simultaneously without a conflict.

# C. Extraction of Field Emission and Thermionic Emission Current Components including SBL

As discussed above, the exact SBL model for FE (8) can only be activated independently of the approximate SBL that is sufficient for thermionic emission (7). To account for this, we have performed several simulations with the different possible options, as described in Figure 2. In this section we describe how the different current components are subsequently extracted. The strategy we employ is to extract the different current components using the models described above and as shown in Figure 2.

This strategy assumes that when comparing the models the basic self-consistent processes are essentially equivalent. For instance,  $I_{\rm TE,woSBL+FE,woSBL}$  vs.  $I_{\rm TE,woSBL+FE,wSBL}$  assume an identical self-consistency in the simulation environment for the component  $I_{\rm TE,woSBL}$ . This is a requirement for the superposition strategy and is valid in a limited range.

# Thermionic Emission with SBL model

Fig. 3. Schottky barrier lowering model for thermionic emission. The dashed lines indicate the barrier height with and without lowering. The red line indicates the approximation used by Sentaurus.

### Field Emission with SBL model

Fig. 4. Schottky barrier lowering model for field emission. The solid black line is the barrier height without lowering and the red line is the barrier lowering used in the Sentaurus FE model.

The following current components are calculated using different Synopsys TCAD models:

$$I_{TE,woSBL}$$

$$I_{TE,woSBL+FE,woSBL}$$

$$I_{TE,woSBL+FE,wSBL}$$

$$I_{TE,wSBL}$$

$$I_{TE,wSBL+FE,approx,wSBL}.$$

(9)

In addition to the different components one finally obtains the overall current including the Schottky barrier lowering by

$$I_{\text{FE,wSBL}} = I_{\text{TE,woSBL+FE,wSBL}} - I_{\text{TE,woSBL}}$$

$$I_{\text{FE,wSBL+TE,wSBL}} = I_{\text{FE,wSBL}} + I_{\text{TE,wSBL}}.$$

(10)

To compare these current components, the following codes are defined to account for the different models:

```

#if @SBL@ == 1

*-Thermionic Emission with SBL

#if @TEFE@ == 0

Physics( Electrode = "source")

{

BarrierLowering(Full)

eThermionic hThermionic

}

*-Thermionic Emission and

*-approx. Field Emission with SBL

#elif @TEFE@ == 1 *

Physics( Electrode = "source")

{

Recombination(BarrierTunneling)

BarrierLowering(Full)

eThermionic hThermionic

}

#endif

```

```

#elif @SBL@ == 0

*-Thermionic Emission without SBL

#if @TEFE@ == 0

Physics ( Electrode = "source")

eThermionic hThermionic

-Thermionic Emission and

*-Field Emission without SBL

#elif @TEFE@ == 1

Physics ( Electrode = "source")

Recombination (BarrierTunneling)

eThermionic hThermionic

*-Thermionic Emission without SBL and

*-Field Emission with SBL

#elif @TEFE@ == 2

Physics ( Electrode = "source")

Recombination (BarrierTunneling (BarrierLowering))

eThermionic hThermionic

#endif

#endif

```

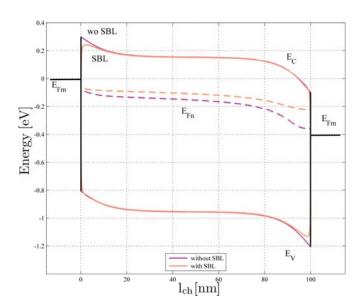

Fig. 5. Investigation of the SBL influence on the band-diagram and quasi-Fermi level of a Si SB-DG-MOSFET with  $\phi_{\rm Bn}=0.3 {\rm eV}.$  Channel device geometry:  $l_{\rm ch}=100{\rm nm},~t_{\rm ch}=20{\rm nm},~t_{\rm ox,SiO_2}=2{\rm nm}.$  Bias conditions:  $V_{\rm ds}=0.4V,~V_{\rm g}=0.4V.$

Furthermore, when analyzing the band edge profiles caution should be employed because even if the models are activated this does not mean that the band edge profiles are visualized using the "real" Schottky barrier lowering effect schown in Figure 4. The SBL for TE shows the maximum shift as given in Figure 3, and the SBL model for FE is not displayed at all, because, as stated above, it is accounted in the simulation path without SBL.

If one wants to observe the real band edge profile a mapping function or script is required, which takes into account the SBL models. Considering these, one has to apply the models as shown in Figure 2 and follow this framework to obtain the different current components.

### V. RESULTS & DISCUSSION

Figure 1 shows the analyzed structure of the Schottky barrier Double-Gate MOSFET device including round corners to avoid singularities at the silicon/oxide interface and increased fields. The results are obtained by the simulation setup presented in [13].

First, a comparison of band-diagram and Fermi level positions with and without SBL is shown in Figure 5. These conditions explain the behavior of the on-current in p-type devices, caused by field and thermionic emission from the source junction. In general the behavior in the middle of the channel and at the silicon/oxide interface is similar, except for the higher fields at the silicon/oxide interface due to the increased electrostatic control of the gate, resulting in higher gradients. An additional DIBL effect results from the SBL effect on the source side for shorter channel lengths.

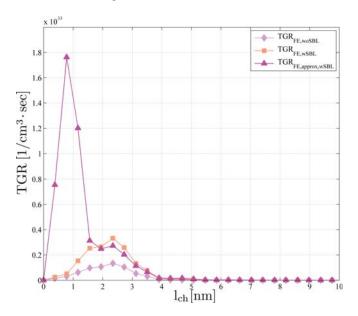

Fig. 6. Comparison of the TGR (TunnelingGenerationRate) at the silicon/oxide interface for the different field emission models. Channel device geometry:  $l_{\rm ch}=100{\rm nm},\,t_{\rm ch}=20{\rm nm},\,t_{\rm ox,SiO_2}=2{\rm nm}.$  Bias conditions:  $V_{\rm ds}=1V,\,V_{\rm g}=1V.$

The band-diagram graph offers several general observations. The bandgap is significantly shifted near the metal-semiconductor interface due to the image-force effect and it becomes larger for smaller devices. We note that quantum effects, which were not included here, will work in the opposite way and increase the bandgap as the device dimensions are decreased. However, in small devices there will be additional barrier lowering due to multiple reflections at the opposite barrier [23]. The quasi-Fermi level for electrons is shifted towards the conduction band and an increased band bending for the junction from the depletion region results. This leads to a decreased tunneling probability, while the quasi-Fermi level acts as counterpart in the opposite way.

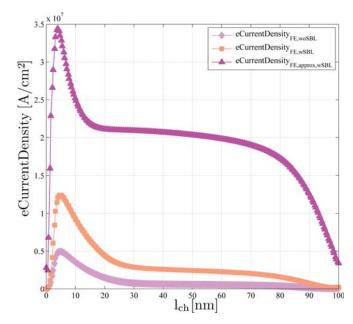

Fig. 7. Comparison of the electron current density at the silicon/oxide interface for the different field emission models. Channel device geometry:  $l_{\rm ch}=100 {\rm nm},$   $t_{\rm ch}=20 {\rm nm},$   $t_{\rm ox,SiO_2}=2 {\rm nm}.$  Bias conditions:  $V_{\rm ds}=1 V,$   $V_{\rm g}=1 V.$

The impact of SBL depends on the nature of the metalsemiconductor interface and determines if field or thermionic emission currents are dominant. We know the importance of these transport mechanisms is a function of the source/drain to gate underlap (here the underlap is zero).

Generally, field emission seems to be the dominant mechanism in some reports [10] and thermionic emission in others [9]. This depends on the barrier height (larger barriers like NiSi  $\approx 0.37 \mathrm{eV}$  will be dominated by field emission, smaller barriers like  $\mathrm{PtSi/ErSi_{2-x}} \approx 0.27 \mathrm{eV} - 0.2 \mathrm{eV}$  will be dominated by thermionic emission) as well as the nature of the metal/semiconductor junction and the subsequent influence of SBL. If no SBL is present, field emission will be the dominant effect, because the higher barrier for the charge carriers will be more difficult to surmount and an increased effect of field emission is to be expected. SBL can change this, where the barrier lowering increases both field and thermionic emission.

Therefore, it is essential to simulate SBL effects accurately because it determines the accuracy and relative importance of field and thermionic emission currents.

Figure 6 shows a comparison of the field emission current (denoted as TunnelingGenerationRate or TGR) without any SBL  $TGR_{FE,woSBL}$ , with image-force SBL  $TGR_{FE,wSBL}$  modeled by equation (8), and  $TGR_{FE,approx,wSBL}$  with simple SBL as modeled by equation (7).

One can clearly see the differences in the field emission current in the first  $10\mathrm{nm}$ . As expected the TGR without SBL  $TGR_{\mathrm{FE,woSBL}}$  shows less field emission due to decreased tunneling probability and further effects [13] due to the higher

barrier height as observed in Figure 5. More of interest is the comparison of the TGR with SBL  $TGR_{\rm FE,wSBL}$  and SBL  $TGR_{\rm FE,approx,wSBL}$ .

The difference is significant and expected from the principal graphs of Figures 3 and 4. The main tunneling contribution for the approximated field emission  $TGR_{FE,approx,wSBL}$  results near the metal-semiconductor interface. This is caused by the increased impact of the quasi-Fermi level and tunneling probability due to the approximation of the conduction band edge. Furthermore, the TGR for the  $TGR_{FE,approx,wSBL}$  is almost one order of magnitude higher than the TGR of  $TGR_{FE,wSBL}$ . Additionally, the maximum of the TGR for  $TGR_{FE,wSBL}$  results at approximately 2.5nm. This correlates to Figure 5, where the maximum of the conduction band edge and quasi-Fermi level occurs at almost the same position.

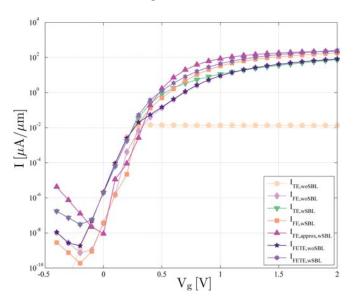

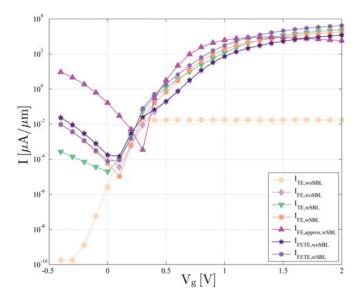

Fig. 8. Investigation of the current components  $I_{\rm FE}-V_{\rm g}$ ,  $I_{\rm TE}-V_{\rm g}$  with and without SBL with  $\phi_{\rm Bn}=0.3 {\rm eV}$ . Channel device geometries for Si SB-DG-MOSFET:  $l_{\rm ch}=100 {\rm nm},~t_{\rm ch}=20 {\rm nm},~t_{\rm ox,SiO_2}=2 {\rm nm}.$  Bias conditions:  $V_{\rm ds}=0.05 V,~V_{\rm g}=-0.5 V$  to 2 V in steps of 0.1 V.

If one compares the electron current densities in Figure 7 without SBL eCurrentDensity\_{FE,woSBL}, with image-force SBL eCurrentDensity\_{FE,wSBL}, and with simple SBL eCurrentDensity\_{FE,approx,wSBL} the analysis comes full circle. The correlation between the TGR and the electron current density is clear and shows that the electron current density for the field emission without SBL case is lowest as expected. Comparing the electron current density for eCurrentDensity\_{FE,wSBL} vs. eCurrentDensity\_{FE,approx,wSBL} it is obvious that the latter leads to an electron current density increase of almost a factor of 2.5x at approximately 5nm from the metal-semiconductor interface.

This leads to an overestimation of the field emission current component as the following transfer characteristics show. In Figure 8 an investigation of the different current components for

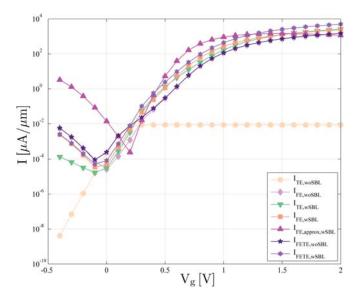

Fig. 9. Investigation of the current components  $I_{FE}-V_g,\,I_{TE}-V_g$  with and without SBL with  $\phi_{\rm Bn}=0.3 {\rm eV}.$  Channel device geometries for Si SB-DG-MOSFET:  $l_{\rm ch}=100 {\rm nm},\,t_{\rm ch}=20 {\rm nm},\,t_{\rm ox,SiO_2}=2 {\rm nm}.$  Bias conditions:  $V_{\rm ds}=1V,\,V_g=-0.5V$  to 2V in steps of 0.1V.

a "long-channel" device with  $l_{\rm ch}=100{\rm nm}$  and  $V_{\rm ds}=0.05V$  are shown. The components are extracted as depicted in Figure 2 and treated according to equation (10).

Fig. 10. Investigation of the current components  $I_{\rm FE}-V_g,\,I_{\rm TE}-V_g$  with and without SBL with  $\phi_{\rm Bn}=0.3 {\rm eV}.$  Channel device geometries for Si SB-DG-MOSFET:  $l_{\rm ch}=22 {\rm nm},\,t_{\rm ch}=10 {\rm nm},\,t_{\rm tox,SiO_2}=2 {\rm nm}.$  Bias conditions:  $V_{\rm ds}=0.8 {\rm V},\,V_g=-0.5 {\rm V}$  to  $2 {\rm V}$  in steps of  $0.1 {\rm V}.$

As one can see and as expected, if the field emission is calculated with the simplified SBL model (equation (7)) an overestimation of the current  $I_{\rm FE,approx,wSBL}$  between  $V_{\rm g}=0.5$  to 1.5V is observed, compared to the current  $I_{\rm FE,wSBL}$  which

was predicted with the image-force SBL model (equation (8)). This is expected and supported by the analysis of Figures 6 and 7. Furthermore, ambipolar leakage (or gate-induced-drain-leakage, GIDL) current is almost two decades larger for the simplified SBL model case, due to overestimation of currents at the drain side. This increase in leakage currents at the drain valence-band edge occurs for the same reasons as the increase of drive currents at the source conduction band edge.

Figure 9 offers a similar investigation of the different current components for a "long-channel" device with  $l_{\rm ch}=100{\rm nm}$  for  $V_{\rm ds}=1V.$  Here it is easily observed that the overestimation in the saturation region is worse. Additionally, it offers different slopes for the field emission region and also produces incorrect results in the higher  $V_g$  regime, where a decrease in current is observed as  $V_g$  increases.

In Figure 10 the different current components are given for a "short-channel" device with  $l_{\rm ch}=22{\rm nm}$  and  $V_{\rm ds}=0.8V.$  Here identical behavior is observed compared to the "long-channel" device of Figure 9 with the exception that the absolute values for the currents and slopes are different. Note that the degradation of the current  $I_{\rm FE,approx,wSBL}$  for higher  $V_{\rm g}$  is less important.

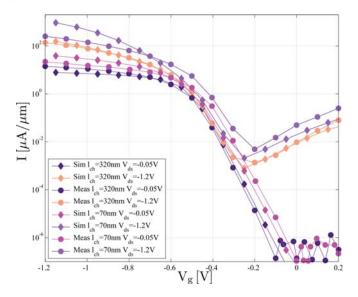

Finally, in Figure 11 the simulation model is compared against experimental data presented in [24] for a PtSi SB-DG-PMOSFET. The model and simulations correlate well with experimental data for channel lengths of  $l_{\rm ch}=320{\rm nm}$  and  $l_{\rm ch}=70{\rm nm}.$

Fig. 11. Comparison of PtSi SB-DG-PMOSFET measurements [24], [25] vs. simulation model.

# VI. CONCLUSION

A framework to manage the available SBL models in Synopsys TCAD Sentaurus for field and thermionic emission was presented. It was shown that a specific application of models is required to accurately predict current components. This can lead to an improvement in the estimation of the off- and on-current regions. The impact on the slope within the field emission region is strongly influenced by the Schottky barrier lowering model selection. The new "image-force" field emission model more accurately accounts for the potential profile near metallic objects and offers new insights in the physical behavior of SB-MOSFETs, while significantly enhancing the possibilities for accurate modeling of these devices. Finally, the simulation model is benchmarked with experimental data.

#### ACKNOWLEDGMENT

The authors would especially like to thank Paul Pfaeffli and Guenther Zandler from Synopsys Inc. for their fruitful discussions and support during the simulation setup.

### REFERENCES

- [1] J. Bruner, "Intel 22nm 3-D Tri-Gate Transistor Technology", News release and press materials (Intel), http://www.intel.com, 2011.

- [2] Q. Liu, et al., "High performance UTBB FDSOI devices featuring 20nm gate length for 14nm node and beyond", *IEDM*, Washington DC, USA, 2013

- [3] J. M. Larson, J. P. Snyder, "Overview and status of metal S/D Schottky-barrier MOSFET technology", *IEEE Transaction Electron Devices* 53 (5), 1048–1058, 2006.

- [4] W. E. Purches, A. Rossi, R. Zhao, S. Kafanov, T. L. Duty, A. S. Dzurak, S. Rogge, and G. C. Tettamanzi, "A planar Al-Si Schottky barrier metal-oxide-semiconductor field effect transistor operated at cryogenic temepratures", *Applied Physics Letters* 107, 2015.

- [5] J. P. Snyder, "Benefits of Schottky Barrier MOS vs. Conventional Doped S/D MOS", Meeting on Schottky Barrier devices, Ueberherrn, Germany, 2016

- [6] S. M. Sze, Kwog K. Ng, "Physics of Semiconductor Devices", John Wiley & Sons, 2007.

- [7] L. E. Calvet, "Electrical Transport in Schottky Barrier MOSFETs", PhD Thesis, Yale University, USA, 2001.

- [8] L. E. Calvet, H. Luebben, M. A. Reed, C. Wang, J. P. Snyder, J. R. Tucker, "Suppression of leakage current in Schottky barrier metal-oxide-semiconductor field-effect transistors", *Journal of Applied Physics 91* (2), 757–759, 2002.

- [9] R. A. Vega, "Comparison study of tunneling models for Schottky field effect transistors and the effect of Schottky barrier lowering", *IEEE Transaction Electron Devices* 53 (7), 1593–1600, 2006.

- [10] J. L. Padilla, L. Knoll, F. Gámiz, Q. T. Zhao, A. Godoy, and S. Mantl, "Simulation of Fabricated 20-nm Schottky Barrier MOSFETs on SOI: Impact of Barrier Lowering", *IEEE Transaction Electron Devices* 59 (5), 1320–1327, 2012.

- [11] "ATLAS User's Manual", SILVACO, Inc., 2010.

- [12] R. A. Vega, and Tsu-Jae King Liu, "A Comparative Study of Dopant-Segregated Schottky and Raised Source/Drain Double-Gate MOSFETs", IEEE Transaction Electron Devices 55 (10), 2665–2677, 2008.

- [13] M. Schwarz, L. E. Calvet, J. P. Snyder, T. Krauss, U. Schwalke, and A. Kloes, "On the Physical Behavior of Cryogenic IV and III-V Schottky Barrier MOSFET Devices", *IEEE Transaction Electron Devices* 64 (9), 3808–3815, 2017.

- [14] "TCAD Sentaurus", Synopsys, Inc., c-2016.12 Edition, 2016.

- [15] A. Schenk and S. Müller, "Analytical Model of the Metal-Semiconductor Contact for Device Simulation", Simulation of Semiconductor Devices and Processes (SISDEP) 5, 441–444, 1993.

- [16] A. Schenk, "Advanced Physical Models for Silicon Device Simulation", Springer, 1998.

- [17] H. A. Bethe, "Theory of Boundary Layer of Crystal Rectifiers", MIT Radiat. Lab. Rep., 1942.

- [18] A. Schenk and G. Heiser, "Modeling and simulation of tunneling through ultra-thin gate dielectrics", Applied Physics Letters 81 (12), 7900–7908, 1997.

- [19] M. Ieong, P. M. Solomon, S.E. Laux, H.-S. P. Wong, D. Chidambarrao, "Comparison of Raised and Schottky Source/Drain MOSFETs Using a Novel Tunneling Contact Model", *IEDM*, 733–736, 1998.

- [20] G. Wentzel, "Eine Verallgemeinerung der Quantenbedingungen für Würfel Zwecke der Wellenmechanik", Z. Physik 38, 518–529, 1926.

- [21] H. A. Kramers, "Wellenmechanik und halbzahlige Quantisierung", Z. Physik 39, 828–840, 1926.

- [22] L. Brillouin, La mécanique ondulatoire de Schrödinger; "une Méthode Générale de resolution durchschnittliche N\u00e4herungswerte successives", Comptes rendus (Paris) 138, 24-26, 1926.

- [23] J. G. Simmons, "Generalized Formula for the Electric Tunnel Effect between Similar Electrodes Separated by a Thin Insulating Film", *Journal of Applied Physics 34* (6), 1963.

- [24] L. Hutin, M. Vinet, T. Poiroux, C. Le Royer, B. Previtali, C. Vizioz, D. Lafond, Y. Morand, M. Rivoire, F. Nemouchi, V. Carron, T. Billon, S. Deleonibus, O. Faynot, "Dual Metallic Source and Drain Integration on Planar Single and Double Gate SOI CMOS down to 20nm: Performance and Scalability Assessment", *IEDM*, 1–4, December, 2009.

- [25] L. Hutin, "Study of Schottky Barrier MOSFETs on SOI, SiGeOI and GeOI Substrates", PhD Thesis, University of Grenoble, France, 2010.

John P. Snyder (S'93—M'95) earned his BS in Aerospace Engineering from MIT in 1988 and his Ph.D. in Electrical Engineering from Stanford University in 1996. His area of specialization is silicon process technology and physics of semiconductor devices. His tenure in this field goes back more than twenty five years. He has worked at Hitachi Central Research Labs in Tokyo, Japan as well as National Semiconductor in Santa Clara, CA. In 1998 he started Spinnaker Semiconductor to develop metal source/drain "Schottky" CMOS technology.

**Tillmann Krauss** received the Diploma degree in electrical engineering and economics from Technical University of Darmstadt. Currently, he is conducting PhD studies at the Institute for Semiconductor Technology and Nanoelectronics in the department of electrical engineering of the Technical University of Darmstadt. His research interests include simulation and fabrication of nanoelectronic devices with special focus on reconfigurable high-temperature capable field effect transistors.

Mike Schwarz (M'15) received the Diploma degree from the University of Applied Sciences Giessen-Friedberg, Giessen, Germany, in 2008, and the M.S. degree in electrical engineering and the Ph.D. (Hons.) degree with a focus on compact modeling of Schottky barrier multiple-gate FETs from the Universitat Rovira i Virgili, Tarragona, Spain, in 2009 and 2012, respectively. His current research interests include Schottky barrier MOSFET devices and compact modeling.

Udo Schwalke (M'94–SM'13) was awarded a Research Fellowship from the Alexander-von-Humboldt-Foundation for his Ph.D. thesis in 1984. During 1984 - 1986, he was appointed Caltech Research Fellow at the California Institute of Technology, USA. In 1987, he joined the Siemens AG, R&D Microelectronics in Munich, Germany. From 1990-1992 he was responsible for the 64Mb DRAM device design at IBM/Siemens, USA. Since August 2001, Dr. Schwalke is Professor in Electrical Engineering and the Managing Director of the Institute of Semiconductor Technology at the TU

Darmstadt. His current research interest focuses on the fabrication of emerging nano-devices.

Laurie E. Calvet (M'97) received a B.S. degree in applied physics from respectively Columbia University (1995) and a Ph.D. from Yale University (2001). In 2007 she joined the French Centre National de la Recherche Scientifique and carries out research at the Center for Nanoscience and Nanotechnology, Université Paris-Sud. Her major fields of research include device physics of semiconductors and nanodevices and more recently hardware implementations of novel computing paradigms.

Alexander Kloes (M'95–SM'16) received the Diploma and Ph.D. degrees in electrical engineering from the Solid-State Electronics Laboratory, Technical University of Darmstadt, Darmstadt, Germany, in 1993 and 1996, respectively. He has been a Professor with Technische Hochschule Mittelhessen, Giessen, Germany, since 2002. His current research interests include modeling of semiconductor devices, especially for nanoscale MOS devices and organic TFT.