# A study on power losses of the 50 kVA SiC converter including reverse conduction phenomenon

### J. RĄBKOWSKI\* and T. PŁATEK

Warsaw University of Technology, Institute of Control and Industrial Electronics, 75 Koszykowa St., 00-662 Warsaw, Poland

**Abstract.** This paper deals with performance of the 50 kVA three-phase converter built with switches based on SiC MOSFET and anti-parallel Schottky diodes. In contrast to popular IGBT converters, a negative switch current is capable of flowing through the reverse conducting transistor, which results in different distribution of power losses among the devices. Thus, equations describing the conduction power losses of the transistor and diode are improved and verified by means of circuit simulations in Saber. Moreover, a comparison of power losses calculated with the use of standard and new equations is also shown. Total power losses in three SiC MOSFET modules of a 50 kVA converter operating at 20 kHz are up to 30% lower when reverse conduction is taken into account. This shows the importance of the discussed problem and proves that much better accuracy in the estimation of power losses and junction temperatures of SiC devices may be obtained with the proposed approach.

Key words: power losses, three-phase converters, MOSFET, Schottky diode, reverse conduction.

#### 1. Introduction

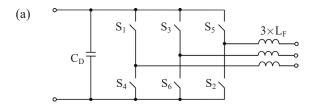

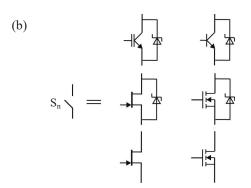

The technology of silicon carbide (SiC) power devices is facing a rapid development in recent years and, in consequence, the area of its application is continuously extending [1, 2]. New diodes and transistors (unipolar JFETs and MOSFETs, as well as bipolar BJTs), available mostly in 1200 V and 1700 V voltage class, can be applied in three-phase converters rated up to several tens of kVAs [2-12]. This field is nowadays dominated by well-established technology of silicon IGBTs, which show different properties in comparison to new SiC power devices. The difference is visible mainly when switching performance is taken into account – SiC devices are able to reach higher dv/ dt and di/dt values. This impacts switching power losses of the converters, but the issue of the on-state behavior and conduction power losses requires to be analysed also from another perspective. Particular attention is required when unipolar SiC transistors (JFETs and MOSFETs) are discussed, while a SiC bipolar transistor operates in widely applied three-phase converter (Fig. 1), in the same way as an Si IGBT. The point is that unipolar transistors, JFETs and MOSFETs alike, display an ability to conduct negative currents through the channel [13]. This feature may be utilized in a synchronous rectification discussed in [14], or design of diode-less converters presented in [15] and then in [16–20]. A three-phase converter without external anti-parallel diodes is a very tempting concept, i.e. due to the reduced operating costs of the power devices. Furthermore, on-state power losses can also be easily expressed, but the most common case is a power switch built with SiC unipolar transistor and anti-parallel SiC Schottky (Fig. 1b). The same can be said about literature examples [3-12] and an offer of the manufacturers providing integrated power modules [4, 10, 12, 25]. From the point of view of on-state power losses, this case is the

most complex as reverse-conducting unipolar transistor shares the current and, in consequence, the power losses with anti-parallel SiC Schottky. Until now, this problem has been studied in terms of circuit simulations in [21] for SiC MOSFETs and, in a much more detailed manner, in [22] for SiC JFETs. The authors of [22] provide careful analysis of the problem and show results of calculations of power losses verified by experiments, but the final equations for conduction power losses are not provided. For design engineers, these equations are essential in the design process of the three-phase power converters, and it has to be stressed that the standard equations, presented for Si IGBTs in late 1980s [23, 24], may result in mismatches when estimating power losses and, finally, junction temperatures. This

Fig. 1. Three-phase converter (a) and possible scenarios of the power switch with Si and SiC devices (b)

Bull. Pol. Ac.: Tech. 64(4) 2016

<sup>\*</sup>e-mail: jacek.rabkowski@ee.pw.edu.pl

may be a serious problem during the design process of threephase converters with new SiC power devices, and especially crucial for converters with conduction losses dominating over the switching losses (i.e. rated at high power). In consequence, the calculated power losses and junction temperatures may be underestimated, which would lead to an incorrect design of the cooling system and possible failures of the operating power converters. Thus, a more detailed study of both the reverse conduction and the impact on power losses is definitely required.

This paper deals with this issue and provides valid equations describing conduction power losses of a three-phase converter controlled with sinusoidal modulation. The new equations are verified by means of circuit simulations conducted in Saber for specific parameters of 1200 V/100 A module. Then, differences between standard and new equations are also shown on the example of the 50 kVA converter to further stress the importance of the discussed problems.

## 2. Power switch based on a SiC unipolar transistor and a Schottky diode in three-phase converter

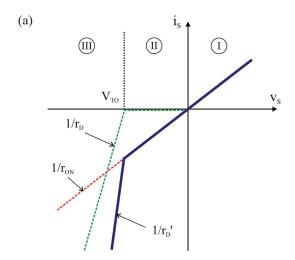

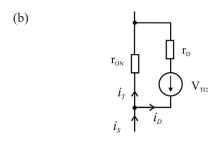

An analysis of the power switch built with SiC unipolar transistor and anti-parallel Schottky diode can be started with the I–V characteristic presented in Fig. 2a. Assuming that the gate-source voltage of the transistor is constant and higher than the threshold value, a unipolar transistor behaves like a resistor

Fig. 2. The I–V characteristics of the switch built with unipolar transistor and Schottky diode (a) and equivalent circuit of this switch in part III (b)

with a linear characteristic (marked with a dashed red line in Fig. 2a). At the same time, the SiC Schottky diode characteristic may also be linearized (dashed green line). The characteristic of the switch (solid blue line) is composed on the base of the transistor and diode characteristics. The three specific parts can be identified in Fig. 2a. At first, for positive switch current  $i_S$ , the dependence between the switch voltage and current is associated to the on-state resistance  $(r_{ON})$ , as only the unipolar transistor is conducting – this part is marked as I. When the current of the switch becomes negative with the voltage drop across the transistor being lower than the threshold voltage of the anti-parallel SiC Schottky  $V_{TO}$ , part II of the characteristic remains linear, as the diode is in the off-state. Finally, when the voltage drop across the transistor is higher than  $V_{TO}$ , both devices conduct, and part III of the characteristic is observed with the slope  $1/r_D$ ' caused by the parallel connection of the onstate resistance  $r_{ON}$  and the dynamic resistance of the Schottky  $r_D$ . An equivalent of the circuit of the switch in this part of the characteristic is presented in Fig. 2b.

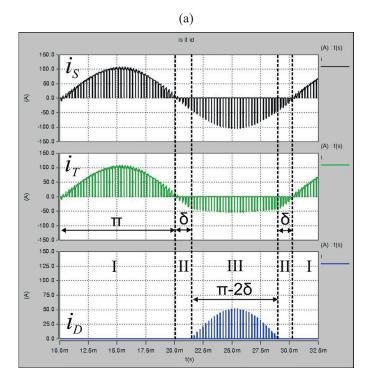

When the discussed switch is employed in a three-phase converter, the aforementioned parts of the I-V characteristics from Fig. 2a are directly transferred into three different operation phases. This issue is illustrated with the results of a Saber simulation (Fig. 3a), where the switch, transistor and diode currents can be noticed for a duration of a single period of the phase current. The converter operating conditions are as follows: DC voltage of 700 V, output power  $S_N = 50$  kVA, power factor close to unity, switching frequency  $f_S = 4$  kHz, modulation index m = 1, dead-time set to zero for better visual clarity. All six switches of the converter in Fig. 1a are simulated with the use of ideal switch and diode models. Waveforms presented in Fig. 3a show the behavior of the switch S<sub>4</sub>. For reference, the exact same waveforms are presented in Fig. 3b for the same switch of the IGBT converter operating under similar conditions.

According to waveforms presented in Fig. 3, the switch current i is positive and flows through the transistor (Fig. 3a) in exactly the same manner as in the case of IGBT (Fig. 3b) during half of the period (related to angle  $\pi$ ). This area is denoted as phase I, in reference to part I of I-V characteristic (Fig. 2a). Then, in phase II, the scenario observed in Fig. 3a is different than in Fig. 3b: the switch current is negative and still flows through the reverse-conducting transistor. The voltage drop across the switch is lower than threshold voltage of the SiC Schottky  $V_{TO}$  and the diode current remains at zero. Two symmetrical periods, described by angle  $\delta$ , can be defined in Fig. 3a, where  $\delta$  is expressed by:

$$\delta = \arcsin \frac{V_{T0}}{r_{ON}I_M} \tag{1}$$

Thus, the duration of phase II depends on the peak phase current  $I_M$  and static parameters of the diode and the transistor. Note that for transistors with very low on-state resistance, or for modules with a number of parallel-connected transistor chips, it is highly possible to witness a scenario where  $\delta = \pi/2$ . But in most cases, when the phase current increases and the transistor

Fig. 3. Three-phase converter operating at 50 kVA and 4 kHz. From the top: current of the switch  $S_4$  ( $i_S$ ), transistor  $T_4$  ( $i_T$ ) and diode  $D_4$  ( $i_D$ ), while  $S_4$  is simulated as a switch built with a diode and (a) unipolar (b) bipolar transistor

voltage becomes higher than  $V_{TO}$ , the diode starts conducting (see part III of I-V characteristics in Fig. 2a), and phase III is observed for the remaining part of the fundamental period (angle  $\pi$ -2 $\delta$ ). Again, the situation is different than in the IGBT case, as the switch current is distributed among two conducting devices. The switch in phase III may be described by the circuit shown in Fig. 2b and it can be found that:

$$i_T = \frac{r_D}{\sum r} i_S + \frac{V_{TO}}{\sum r} \tag{2}$$

$$i_D = \frac{r_{ON}}{\sum_r} i_S - \frac{V_{TO}}{\sum_r} \tag{3}$$

where  $\Sigma \mathbf{r} = r_{ON} + r_D$ .

Bull. Pol. Ac.: Tech. 64(4) 2016

This means that the actual value of the current in the transistor and diode in phase III depends not only on the phase current, but also on the temperature-related parameters of the devices. All three of the values are changing during converter operation, and therefore, the distribution of currents among the devices is expected to also be variable.

### 3. Improved equations describing conduction power losses in three-phase converter

Current waveforms of the transistor and diode shown in Fig. 3a and Fig. 3b are different, which leads to the conclusion that the equations describing conduction power losses in IGBT and forward diode, proposed in 1980's [23, 24], do not fit the case of a switch built with SiC FET and Schottky. These standard equa-

tions were determined under the assumption that the positive current flows through the IGBT, and the negative one through the diode. For a common sinusoidal modulation, power losses caused in the transistor and diode are expressed as [23, 24]:

$$P_{C_{\_IGBT}} = \frac{1}{2} \left( V_{CE0} \frac{I_m}{\pi} + r_T \frac{I_m^2}{4} \right) + \\

+ m \cos \varphi \left( V_{CE0} \frac{I_m}{8} + \frac{1}{3\pi} r_T I_m^2 \right)$$

(4)

$$P_{C_{-}D} = \frac{1}{2} \left( V_{T0} \frac{I_m}{\pi} + r_D \frac{I_m^2}{4} \right) - m \cos \varphi \left( V_{T0} \frac{I_m}{8} + \frac{1}{3\pi} r_D I_m^2 \right)$$

(5)

According to Fig. 3a, in the case of the discussed switch with a SiC unipolar transistor and Schottky diode, conduction power losses of the transistor  $P_{CT}$  will occur in all three phases:

$$P_{CT} = P_{CT}^{I} + P_{CT}^{II} + P_{CT}^{III}$$

(6)

But from the characteristic shown in Fig. 2a and current waveforms in Fig. 3a, it is clear that the equation is different for each phase. From the same figures, it can be seen that the diode dissipates conduction power losses only during phase III:

$$P_{CD} = P_{CD}^{III} \tag{7}$$

The behavior and waveforms of the SiC unipolar transistor and IGBT during phase I are exactly the same. Thus, a simplified

equation (4) may be applied to express the conduction power losses in the transistor:

$$P_{CT}^{I} = r_{ON} I_m^2 \left( \frac{1}{8} + \frac{m \cos \varphi}{3\pi} \right)$$

(8)

For phase II the transistor power losses occur during two time periods (angle  $\delta$ , see Fig. 3a), which leads to an equation:

$$P_{CT}^{II} = \frac{r_{ON}I_m^2}{4\pi} \begin{pmatrix} \sigma - \frac{1}{2}\sin 2\sigma + \\ +\frac{m\cos\varphi}{6} (9\cos\sigma - \cos 3\sigma - 8) \end{pmatrix}$$

(9)

Note that for a special case  $\delta = \pi/2$  (when diode is not conducting), Eq. (9) becomes equal to (5), simplified after assumption that  $V_{T0} = 0$  and  $r_{ON} = r_D$ . This confirms that (9) is valid. Definitely the most complex scenario is the one observed in phase III, as both devices share the current and, in result, the conduction power losses. Assuming resistive behavior of the transistor and linearized characteristic of the diode (Fig. 2b) it is possible to determine an equations (10) and (11). Again, both equations may be verified for the special case  $\delta = \pi/2$  when

phase III does not occur. The conduction power losses calculated from (10) and (11) for  $\delta = \pi/2$  are equal to zero which confirms that all three equations are correct.

#### 4. Circuit simulations in Saber

In this section, all equations describing the conduction power losses of the switch built with SiC MOSFETs and Schottky diodes are verified by comparing numerical calculations performed in Matlab to measurements conducted in Saber circuit simulator. The parameters of a three-phase converter are the same as in Section II ( $V_{DC} = 700 \text{ V}$ , S = 50 kVA, m = 1), with only the power factor fluctuating within the range of -1 to 1. Moreover, the parameters of the real module (1200 V/100 A SiC MOSFET and Schottky [25]) were applied. At first, the thermal characteristics of the SiC MOSFET and SiC diode were developed based on the module datasheet [25] and the parameters of the devices were determined ( $r_{ON} = 16.5 \text{ m}\Omega$  for  $T_{JT} = 72^{\circ}\text{C}$  and  $V_{TO} = 0.859 \text{ V}$ ,  $v_D = 12.2 \text{ m}\Omega$  for  $T_{JD} = 59^{\circ}\text{C}$ ). Then, the conduction power losses of a single transistor and diode were calculated using Matlab and (8-11) – see results in Table 1. In

$$P_{CT}^{III} = \frac{r_{ON}}{2\pi\Sigma r^{2}} \begin{bmatrix} V_{TO}^{2} \left(\frac{\pi}{2} - \sigma - m\cos\varphi\cos\sigma\right) + r_{D}V_{TO}I_{m} \left(2\cos\sigma + m\cos\varphi\left(\sigma - \frac{\pi}{2} - \frac{1}{2}\sin(2\sigma)\right)\right) + m\cos\varphi\left(\sigma - \frac{\pi}{2} - \frac{1}{2}\sin(2\sigma)\right) + m\cos\varphi\left(\sigma - \frac{\pi}{2} - \frac{1}{2}\sin(2\sigma)\right) + m\cos\varphi\left(\cos^{2}\theta - \frac{\pi}{2} - \frac{$$

$$P_{CD}^{III} = \frac{r_{ON}}{2\pi\Sigma r^2} \left[ -V_{TO}^{2} \left( \frac{\pi}{2} - \sigma - m\cos\varphi\cos\sigma \right) + \frac{r_{ON} - r_{D}}{2} V_{TO} I_{m} \left( 2\cos\sigma + m\cos\varphi\left(\sigma - \frac{\pi}{2} - \frac{1}{2}\sin(2\sigma) \right) \right) + \frac{r_{D}r_{ON}}{2} \left( \frac{\pi}{2} - \sigma + \frac{1}{2}\sin2\sigma + \frac{m\cos\varphi}{6} (\cos3\sigma - 9\cos\sigma) \right) \right]$$

(11)

Table 1 Results of calculations and simulations for a 50 kVA converter ( $m=1, V_{DC}=700 \text{ V}, r_{ON}=16.5 \text{ m}\Omega, V_{TO}=0.859 \text{ V}, r_D=12.2 \text{ m}\Omega$ ), all values per transistor or diode

|      | Calculations in Matlab [W] |              |                               |                |              | Measurements in Saber [W] |                              |                               |                                |          | Error [%]    |                |                |                 |

|------|----------------------------|--------------|-------------------------------|----------------|--------------|---------------------------|------------------------------|-------------------------------|--------------------------------|----------|--------------|----------------|----------------|-----------------|

| cosφ | P <sub>CT</sub>            | $P_{CT}^{I}$ | P <sub>CT</sub> <sup>II</sup> | $P_{CT}^{III}$ | $P_{\rm CD}$ | P <sub>CT</sub>           | P <sub>CT</sub> <sup>I</sup> | P <sub>CT</sub> <sup>II</sup> | P <sub>CT</sub> <sup>III</sup> | $P_{CD}$ | $P_{CT}^{I}$ | $P_{CT}^{ II}$ | $P_{CT}^{III}$ | P <sub>CD</sub> |

| -1   | 27,4                       | 3,28         | 1,81                          | 22,3           | 6,90         | 27,2                      | 3,25                         | 1,75                          | 22,2                           | 6,70     | 0,8          | 3,5            | 0,6            | 2,1             |

| -0.5 | 31,2                       | 12,5         | 1,57                          | 17,2           | 5,19         | 31                        | 12,4                         | 1,52                          | 17,1                           | 5,11     | 1            | 3,2            | 0,2            | 1,7             |

| 0    | 35,0                       | 21,7         | 1,31                          | 12,0           | 3,57         | 35,2                      | 22                           | 1,36                          | 11,9                           | 3,51     | 1,3          | 3,4            | 1              | 1,7             |

| 0.5  | 38,8                       | 30,9         | 1,06                          | 6,86           | 1,95         | 38,5                      | 30,6                         | 1,08                          | 6,90                           | 1,92     | 1            | 1,6            | 0,6            | 1,5             |

| 1    | 42,6                       | 40,1         | 0,81                          | 1,71           | 0,34         | 42,2                      | 39,7                         | 0,79                          | 1,74                           | 0,35     | 0,9          | 2,4            | 1,9            | 3               |

the next step, the parameters of the aforementioned devices were introduced into the circuit in Saber, and power losses of the diode and transistor were measured for the same conditions – all results are shown in Table 1. The observed differences suggest that the circuit simulation results confirm the calculations performed with the use of the new equations - differences are not higher than 3.5% and decrease as the measured values increase. For the analyzed 50 kVA converter example, the component  $P_{CT}^{II}$  shows very low values (below 1.75 W in all of the cases) and therefore, the obtained difference is the highest, but still on an acceptable level. On the other hand, the component  $P_{CT}^{I}$  changes from 3.25 to 40.1 W, with the variation of power factor, and the difference between calculations and measurement remaining below 1% in most cases. This implies that minor differences are caused by errors introduced during measurements in Saber, or impact of current ripples in simulated circuit, rather than by mistakes in the proposed equations. All in all, the presented comparison confirms that equations (8–11) are valid.

### 5. Impact of the reverse conduction on power losses distribution

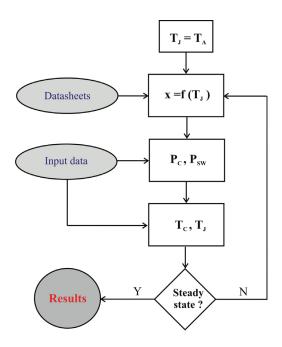

This section shows how the reverse conduction influences power losses and junction temperatures of the power devices on the example of the three-phase 50 kVA converter. The power losses and junction temperatures were determined by means of combined electro-thermal calculations (Fig. 4). It is well known that some electrical parameters of the modules are influenced by the junction temperature, and it

Fig. 4. Idea of the electro-thermal calculations of the power losses and junction temperatures

is necessary to perform calculations in both the electrical and thermal domains. The procedure applied in Matlab starts when junction temperature equals the ambient temperature (here 25°C), which serves as a base to finding actual values of the thermal-dependent parameters (on-state resistances, voltages, switching energies etc., marked as x = f(Tj) in Fig. 4). At this point, it requires a certain amount of effort to find and linearize suitable parameters from the power module datasheet [25]. These parameters, together with the input values (nominal power, DC-link voltage, switching frequency, power factor etc.) are then applied to determine the conduction and switching losses in diodes and transistors. Note that all obtained values are averaged over a single fundamental period of the phase current. In the next step, the heatsink, case and junction temperatures are calculated using thermal resistances of the power modules and the heatsink. The whole procedure is repeated until the analyzed system (the converter with heatsink) reaches a computational steady-state (when the changes of the junction temperature between iterations get lower than 0.5°C). It is believed that the obtained results reflect the behavior of a real circuit, but it has to be underlined once again, that all power loss and temperature values are averaged over a fundamental period of the phase current. The conduction and switching power losses, as well as junction temperatures of diodes and transistors were calculated on the grounds of electro-thermal characteristics of the 1200 V/100 A SiC MOSFET module [25] (by defining changes of parameters dependent on junction temperatures  $r_{ON}$ ,  $V_{TO}$ ,  $r_D$ , but also switching energies of transistors  $E_{ON}$ ,  $E_{OFF}$ ) and thermal resistances. Power factors  $(\cos\varphi)$  and thermal resistance of a common heat-sink  $(R_{TH})$ were varying, while the modulation index, input voltage and switching frequency were constant (m = 1,  $V_{DC} = 700 \text{ V}$  and  $f_S = 20 \text{ kHz}$ ).

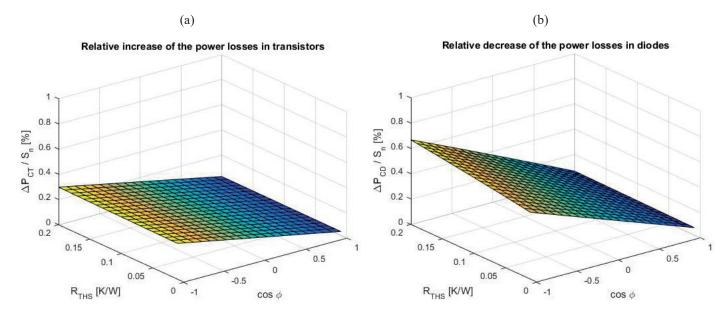

At first, the standard equations (4, 5) were applied under the assumption that the transistors are turned-off during the negative currents and reverse conduction does not occur. Then, exactly the same electro-thermal calculations were repeated, but with the new equations (8–11) including reverse conduction of the transistors. Finally, the obtained differences between the conduction power losses using standard and new equations were plotted versus the displacement power factor  $(cos\varphi)$  and thermal resistance of the common heatsink  $(R_{THS})$ - see Figs. 5 and 6. All results are related to the nominal power of the converter (50 kVA), and the presented differences are expressed as percentage. Note that figures show influence of the reverse conduction on the distribution of power losses. After an analysis of the calculations visible in Fig. 5, it is clear that the conduction power losses increase in the transistor (0.03 to 0.3% of  $S_N$ ) and decrease in the diode (0.06 to 0.68% of  $S_N$ ) when the reverse conduction phenomenon is taken into account. This observation is in agreement with presented above analysis and the waveforms observed in Fig. 3. Moreover, this effect is more visible for the negative values of the displacement power factor  $(\cos\varphi)$  than for the positive values, as for the negative ones, the amount of the reverse current is much higher.

Fig. 5. Calculated deviation of the conduction power losses due to reverse conduction in reference to converter nominal power: increase in transistors (a) and decrease in diodes (b) (20 kHz/50 kVA three-phase converter with three 1200 V/100 A SiC MOSFET modules)

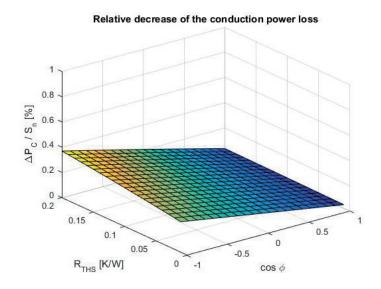

For the analyzed 50 kVA converter, the total conduction losses are reduced over the whole operation range kVA, as can be seen in Fig. 6. This means that the difference between the diode conduction power losses expressed by standard (5) and new equation (11) is more significant than additional transistor losses, defined as the components  $P_{CT}^{II}$  and  $P_{CT}^{III}$  by equations (9) and (10). Again, the difference of the conduction power losses is most significant for negative values of displacement power factor  $(cos\varphi)$ , and is rising together with a rising thermal resistance of the common heatsink. The absolute difference of the calculated conduction power loss is between 14W  $(cos\varphi = 1, R_{THS} = 0.01 \text{K/W})$  and 190 W  $(cos\varphi = -1, R_{THS} = 0.01 \text{K/W})$  and 190 W  $(cos\varphi = -1, R_{THS} = 0.01 \text{K/W})$

912

$R_{THS} = 0.2$  K/W) in all three modules of the 50 kVA three-phase converter. This refers to a decrease of the total power losses (including switching at  $f_S = 20$ kHz) between 4 and 30%, which is a noticeable value. Thus, a possible overestimation of the power calculations may be almost one third when standard equations are applied.

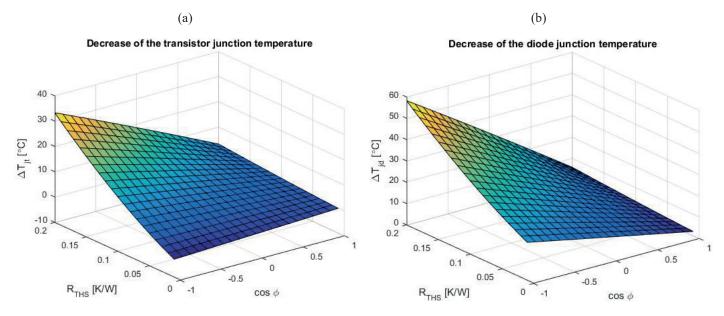

Different values of power losses lead to different junction temperatures of the devices obtained during electro-thermal calculations. The estimated diode junction temperature is seriously reduced (by 2 to 60°C) when reverse conduction is taken into account, as is illustrated in Fig. 7. In addition to this, the transistor junction temperature also decreases almost

Fig. 6. Calculated decrease of the power losses due to reverse conduction in reference to converter nominal power (20 kHz/50 kVA three-phase converter with three 1200 V/100 A SiC MOSFET modules)

Fig. 7. Calculated decrease of the transistor (a) and diode (b) junction temperature due to reverse conduction (20 kHz/50 kVA three-phase converter with three 1200 V/100 A SiC MOSFET modules)

for the whole analyzed area, in spite of the increase in the transistor conduction power loss. The reason is that for the considered model, the increase of the transistor temperature is lower than the corresponding decrease of the case temperature caused by the reduced total power losses. All in all, the steady-state operating point of the converter is different when reverse conduction is taken into consideration, especially for negative power factor and high thermal resistance of the common heatsink.

### 6. Summary

This paper has presented the impact of the reverse conduction on power losses distribution in 50 kVA three-phase converter built with SiC MOSFETs and Schottky diodes. As the transistors can conduct reverse currents, a part of the current, and in consequence, the power loss is moved from the diode towards the transistor. New, improved equations describing conduction losses for sinusoidal pulse width modulation have been presented and verified by means of the Saber circuit simulations. A very good correspondence of the results of the calculations and the simulations has been shown, with error below 3.5%. The novel equations were also applied into electro-thermal simulations in Matlab in order to illustrate the impact of reverse conduction on the performance of the three-phase converter. It was found that the decrease of the diode loss is more significant than the corresponding increase of the transistor loss. In consequence, the total losses are lower by up to 190 W for the 50 kVA converter operating at 20 kHz, which indicates a reduction by 30%. Finally, it has been also shown that the junction temperatures are also different when reverse conduction is taken into account. Thus, the discussed problem is noticeable, and all issues presented in this paper may help in the design process of three-phase converters with SiC power devices as more accurate estimations of the power losses and junction temperatures can be performed.

#### REFERENCES

- J. Milan, P. Gondignon, X. Perpina, A. Perez-Tomas, and J. Rebollo, "A survey of wide bandgap power semiconductor devices", *IEEE Transactions on Power Electronics* 29 (5), 2155–2163 (2014).

- [2] J. Rabkowski, D. Peftitsis, H.P. Nee, "SiC power transistors a new era in power electronics is initiated", *IEEE Industrial Electronics Magazine* 6(2), 17–26 (2012).

- [3] R. Lai et al., "A high-power-density converter", *IEEE Industrial Electronics Magazine* 4 (4), 4–12 (2010).

- [4] T.J. Han, J. Nagashima, S.J. Kim, S. Kulkarni, F. Barlow, "High density 50 kW SiC inverter systems using a JFET based six-pack power module", 8th International Conference on Power Electronics and ECCE Asia, 764–769 (2011).

- [5] F. Xu, T.J. Han, D. Jiang, L.M. Tolbert, F. Wang, J. Nagashima, S.J. Kim, S. Kulkarni, F. Barlow, "Development of a SiC JFET--based six-pack power module for a fully integrated inverter", *IEEE Transactions on Power Electronics* 28 (3), 1464–1478 (2013).

- [6] J. Rabkowski, D. Peftitsis, H.P. Nee, "Design steps towards a 40- kVA SiC JFET inverter with natural-convection cooling and an efficiency exceeding 99.5%", *IEEE Transactions on In*dustry Applications 49(4), 1589–1598 (2013).

- [7] F. Alkayal, J.B. Saada, "Compact three phase inverter in silicon carbide technology for auxiliary converter used in railway applications", 15th European Conference on Power Electronics and Applications EPE-ECCE Europe (2013).

- [8] B. Whitaker et al., "A high-density, high-efficiency, isolated on-board vehicle battery charger utilizing silicon carbide power devices", *IEEE Transactions on Power Electronics* 29 (5), 2606–2617 (2014).

- [9] B. Wrzecionko, B. Bortis, J.W. Kolar, "A 120°C ambient temperature forced air-cooled normally-off SiC JFET automotive inverter system", *IEEE Transactions on Power Electronics* 29 (5), 2345–2358 (2014).

- [10] J. Rice, J. Mookken, "Economics of high efficiency SiC MOSFET based 3-ph motor drive", *Proc. of PCIM Europe*, 1–8 (2014).

- [11] T. Friedli, M. Hartmann, J.W. Kolar, "The essence of three-phase PFC rectifier systems – part II", *IEEE Transactions on Power Electronics* 29 (2), 543–560 (2014).

- [12] J. Colmenarez, D. Peftitsis, G. Tolstoy, D.P. Sadik, H.P. Nee, J. Rabkowski, "High-efficiency 3-phase inverter with SiC MOSFET power modules for motor-drive applications", *Energy Conversion Congress and Exposition*, 468–474 (2014).

- [13] D.C. Sheridan, K. Chatty, V. Bondarenko, J.B. Casady, "Reverse conduction properties of vertical SiC trench JFETs", 24th International Symposium on Power Semiconductor Devices and ICs, 385–388 (2012).

- [14] T. Funaki, M. Matsushita, M. Sasagawa, T. Kimoto, T. Hikihara, "A study on SiC devices in synchronous rectification of DC-DC converter", Twenty Second Annual IEEE Applied Power Electronics Conference, 339–344 (2007).

- [15] B. Ållebrand, H-P Nee, "On the choice of blanking times at turn-on and turn-off for the diode-less SiC JFET inverter bridge", European Conference on Power Electronics and Applications (2001).

- [16] R.A. Wood, Urciuoli D.P., Salem, T.E., Green, R., "Reverse conduction of a 100 A SiC MOSFET module in high-power applications", *Applied Power Electronics Conference and Exposition*, 1568–1571 (2010).

- [17] C. Cai, W. Zhou, K. Sheng, "Characteristics and application of normally-off SiC-JFETs in converters without antiparallel diodes", *IEEE Transactions on Power Electronics* 28 (10), 4850–4860 (2013).

- [18] R. Ouaida, X. Fonteneau, F. Dubois, D. Bergogne, F. Morel, H. Morel, S. Oge, C. Bretagne, Z. A. Le Piquet, "SiC vertical JFET pure diode-less inverter leg", *Applied Power Electronics Conference and Exposition*, 512 – 517 (2013).

- [19] G. Kampitsis, P. Stefas, N. Chrysogelos, S. Papathanassiou, S.Manias, "Assessment of the reverse operational characteristics of SiC JFETs in a diode-less inverter", 39th Annual Conference of the IEEE Industrial Electronics Society, 477–482 (2013).

- [20] H. Liu, H. Wu, Y. Lu, Y. Xing, K. Sun, "A high efficiency inverter based on SiC MOSFET without externally antiparalleled diodes", *Twenty-Ninth Annual IEEE Applied Power Electronics Conference and Exposition*, 163–167 (2014).

- [21] D. Han, J. Noppakunkajorn, B. Sarlioglu, "Analysis of a SiC three-phase voltage source inverter under various current and power factor operations", 39th Annual Conference of the IEEE Industrial Electronics Society, 447–450 (2013).

- [22] X. Fonteneau, F. Morel, C. Buttay, H. Morel, P. Lahaye, "Predicting static losses in an inverter-leg built with SiC normally-off JFETs and SiC diodes", *Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition*, 2636 2642 (2013).

- [23] L.K. Mestha, P.D. Evans, "Analysis of on-state losses in PWM inverters", *IEE Proc.*, 136B (4) 189–195 (1989).

- [24] F. Casanellas, "Losses in PWM inverters using IGBTs", IEE Proc. -Electr. Power Appl., 141 (5), 235–239 (1994).

- [25] CAS100H12AM1 datasheet rev. B, www.cree.com/power.

914 Bull. Pol. Ac.: Tech. 64(4) 2016