genetic algorithms, medical devices, simulation of digital circuits, pseudorandom testing

# Miłosław CHODACKI<sup>\*</sup>, Dariusz MICHALSKI<sup>\*</sup>

# GENETIC ALGORITHMS IN PSEUDORANDOM TESTING OF MEDICAL DIGITAL CIRCUITS

In this paper the problem of unsatisfactory diagnostic efficiency of pseudorandom testing (PRT) technique used to detect faults of digital circuits in testing medical systems of critical importance is presented. The simulations have revealed a weakness of commonly used PRT technique that generally does not assure that all stuck at faults are detected. Thus, it is suggested that PRT technique should be supplemented with additional deterministic testing sequences to enhance fault detection. To design built-in self-testing (BIST) structures a genetic algorithm and digital system stochastic model were used. By employing the stochastic model it is possible to reduce considerably the computer simulation time required for BIST architecture design. In particular, an effect of proportional and ranking selections on the convergence of genetic algorithm in searching for a globally optimal solution, while maintaining the diversity of the population of individuals and limiting its premature stagnation.

## 1. INTRODUCTION

The increasing scale of integration for digital systems, increasing timing frequency, the use of CMOS technique for manufacture of such systems, especially for VLSI systems and decreasing degree of testability caused that the traditional testing techniques employing automatic test equipment (ATE) highly lost its significance. The problem of digital system testing, in particular for sequential systems equipped with a memory module (MM), became such important that the special system solutions, for example BILBO (Built-in Logic Block Observer), scan paths (SP), boundary scan paths (BSP) enabling access to hard-to-test system nodes, thus enhancing the testing process, are employed as early as at the system logic design phase. The digital system design technique that involves testing needs, thus facilitating the testing process is generally referred to as Design for Testability (DFT) [8], [5], [7].

Contrary to combinational systems, the fault detection in sequential systems requires a fault to be stimulated and an error signal to be sent to an externally accessible system primary output. Only such information in the form of an error indicates a failure of a digital system, however this requires a specified activating and output sequences to be selected. There is a wide class of faults related to the digital system design, manufacturing and use. These include, for example, traditional stuckat line faults as well as CMOS transistor Stuck On and Stuck Off faults, open line, bridging and delay faults and even those that generate no logical values. Another division applies to permanent and temporary faults. This paper focuses on Stuck at 0 or Stuck at 1 faults. The Single Stuck at Line (SSL) Model includes tens percents of faults for CMOS systems [5].

There are numerous techniques for determining tests of digital systems, including structural (deterministic), behaviourist (functional), thorough (exhaustive) as well as random and pseudorandom testing. Pseudorandom testing (PRT) is used in the case of Built-in Test (BIST) systems due to a small area overhead of a tester, self-testing ability – generally without operating parameter degradation of the tested system and an acceptable level of SSL fault detection in typical applications. A difficulty consisting in some stagnation in detection of 'resistant' faults is a PRT characteristic. This means that 'resistant' faults require stimulation with a considerably longer test sequence, thus prolonging the testing time. Sometimes such prolonged pseudorandom tests are unable to detect some faults, as they require specific deterministically specified sequences as mentioned above.

Principally there are two BIST techniques - linear and nonlinear. The linear technique makes use of independent Test Pattern Generators (TPG) and Test Response Compactors (TRC). The less common nonlinear technique employs Self-Test Path (STP) or Circular Self-Test Path (CSTP). Obviously, there are also modifications of these structures, for example Condensed Circular Self-Test Path (C2STP). Generally PRT involves the system response signature analysis. The signature in the form of a bit sequence is available at the end of testing session and enables the tested system to be classified as operational or non-operational. Due to TRC loss compression it might happen that some covered faults have been detected but information about such coverage was lost during the testing session. This phenomenon is referred to as fault masking (Aliasing). It was found that fault masking decreases asymptotically with n - the number of comparable bits (most often equal to the compactor

length) to the value of  $2^{-n}$  [6]. In certain circumstances for a compactor of sufficient length, fault masking can be omitted as negligible. When considering fault masking one can say about True Fault Coverage (TFC) instead of Fault Coverage (FC). This nomenclature is however not obligatory, so FC is to be hereinafter understood as TFC.

The problem of BIST structure design, as a STP or CSTP modification will be resolved with a genetic algorithm [4] that is counted among the universal global optimization methods. Genetic algorithms have been successfully applied to solve numerous difficult technical problems, also to applications similar to those presented here [4],[9]. In this paper an effect of both proportional and ranking selections on the convergence of algorithm and maintenance of the population of individuals that codes the BIST structure.

<sup>\*</sup> University of Silesia. Institute of Informatics, 41-200 Sosnowiec, Będzińska 39, Poland, e-mail: miloslaw.chodacki@us.edu.pl, dariusz.michalski@us.edu.pl

#### MEDICAL DEVICES AND TECHNOLOGIES

To enhance FC it is suggested to supplement a pseudorandom test with a deterministic test being stimulated by the ATE tester external system or embedded inside an additional memory module, e.g. ROM, of the tested system. For digital systems used in medicine such as cardio-monitoring, medical robots, defibrillators, electrocardiographs, measuring server and other systems crucial to health-care, an increasing fault coverage is of utmost importance.

There is another class of software faults being increasingly important in the terms of testing (mutational testing, extreme programming technique, etc) not considered in this paper as being covered by software engineering.

# 2. BIST STRUCTURE

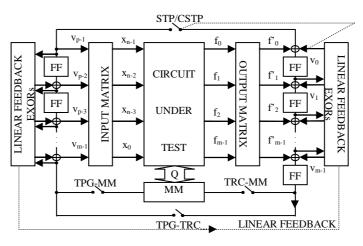

BIST structure presented in Fig. 1 provides more configuration possibilities than standard STP and CSTP. The overhead means used to affect the self-test structure are not connected with the testing procedure but with test simulation only. The simulation is here a method for assessing the BIST structure design based on STP and CSTP.

Fig. 1. BIST structure

where:

$v_0,...,v_{p-1}$  - output register cells, *FF* - cells of register (D or T-type flipflops),  $x_0,...,x_{n-1}$  - circuit inputs,  $f_0,...,f_{m-1}$  - circuit outputs,  $f'_0,...,f'_{m-1}$  - CUT system output signals modified with OM,

The function of STP/CSTP with considering no effect of IM and OM connection matrices can be expressed as follows (1):

$$\begin{bmatrix} V_{0}(t+1) \\ V_{1}(t+1) \\ V_{2}(t+1) \\ \vdots \\ V_{m-1}(t+1) \\ \vdots \\ V_{m}(t+1) \\ \vdots \\ V_{m+p-2}(t+1) \\ V_{m+p-1}(t+1) \end{bmatrix} = T \bullet \begin{bmatrix} V_{0}(t) \\ V_{1}(t) \\ V_{2}(t) \\ \vdots \\ V_{m-1}(t) \\ V_{m}(t) \\ \vdots \\ V_{m+p-2}(t) \\ V_{m+p-1}(t) \end{bmatrix} \oplus \begin{bmatrix} 0 \\ f_{0}\left(V_{m-1}(t), \dots, V_{m+p-2}(t), V_{m+p-1}(t)\right) \oplus V_{0}(t) \\ f_{1}\left(V_{m-1}(t), \dots, V_{m+p-2}(t), V_{m+p-1}(t)\right) \\ \vdots \\ f_{m-1}\left(V_{m-1}(t), \dots, V_{m+p-2}(t), V_{m+p-1}(t)\right) \\ 0 \\ \vdots \\ 0 \\ 0 \end{bmatrix}$$

(1)

where T is a square matrix of register connections.

The STP and CSTP efficiency depends primarily on [1]:

- initial state of STP/CSTP and MM (for sequential systems),

- circuit diagram for connections between STP/CSTP and the tested CUT system. The diagram depends on the input and output connection matrices (IM and OM),

- test sequence length,

- STP/CSTP structure length.

Further information on BIST structure is available in publications [1],[2],[3].

### 3. STOCHASTIC MODEL

FC is highly dependent on the testing sequence length [2],[3]; obviously FC depends also on other parameters, among other things on the function of the tested system, BIST structure initial state, etc. Unfortunately, the relationship between FC and the testing sequence length simulated by a BIST structure is not a functional but stochastic one. Thus, it is impossible to say about a strict and unique relationship between these parameters and only about a probability distribution expressed with a random variable frequency function - FC. To determine FC values the full BIST structure simulation is required while considering all defined faults for the tested system. However, searching for a test sequence of specified length requires a BIST structure simulation on the free from damage system. For a relatively simple synchronous sequential system s298 used in our experiment, it is possible to simulate up to 308 different BIST structures, including 308 defined faults for this system within the FC time (full simulation). Obviously, the stochastic model of the tested system must be previously made accessible. This is a key feature for a considerable reduction of the BIST structure design time.

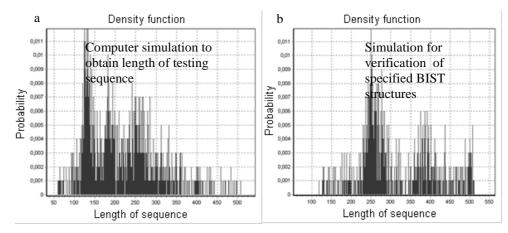

Fig. 2 presents the probability density functions for those test sequences that enable fault coverage at the set level, here FC=0.7 at least. The diagram shown in Fig.3a comes from a simulation is derived from a programmed testing procedure not related to a specified BIST structure. Fig. 3b presents a simulating verification for specified autonomous structures. The graphs can be considered to be similar to each other and to Poisson distribution. Thus, it is possible to replace a time consuming FC simulation with finding a test sequence of appropriate length, o more properly a simulating BIST structure. In the case of the s298 system, a sequence of the length of 512 enables fault detection at the level of FC=0.7 with the probability close to 1.

Fig. 2. Generalized stochastic model of the s298 system for FC=0.7 a –for generalized software structure, b – for a specified self-testing structure (verification)

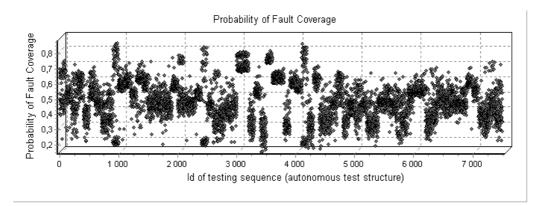

Fig. 3 presents a graph illustrating the relationship between the test sequence length and the BIST structure type which was simulated. One can find that the test sequence length is highly dependent on the BIST structure that enables simulation. It is possible to find those BIST structures (e.g. 3 000 - 4 000) that simulate short test sequences and others stimulating test sequences of values from wider intervals.

Fig. 4 illustrates the relationship between FC and the BIST structure type in which it has been determined. It follows from the figure that various BIST structures can detect faults at different levels within a narrower or wider intervals. There are however certain clusters of relatively narrow intervals of achieved FC values for specified BIST structure types Hence, do exist the BIST structure types of high correlation between FC and the test sequence length stimulated by them. This additional concentration parameter (high correlation) can be included to be a kind of designed BIST structures.

There are important conclusions to be drawn from these figures looked together. One can find that do exist BIST structures stimulating test sequences of short length that however enable high FC to be achieved (e.g. structures  $3\ 000 - 4\ 000$ ). More important observation is that test sequences of large length enable fault coverage also at the high level. This is why the genetic algorithm we use will search for BIST structures allowing stimulation of the longest test sequences. Then, the probability of FC of sufficiently large value acceptable to the system designer will be close to 1 - i.e. nearly sure.

Except the concentration effect mentioned above it is possible to introduce also in the design evolutionary process a parameter determining coexistence of clusters and BIST structures stimulating as short as possible test sequences enabling fault coverage at an acceptable high level. Please notice that the type of structure 3 500, despite the fact that it stimulates short sequences of the length of approx. 50 (Fig. 4), allows FC to be reached at the very high level of about 0.8. This structure represents the simplest shift register (SR) working as STP with unit connection matrices IM and OM that do not modify configuration of connections between STP and the tested system.

Fig. 3. Length of testing sequence vs. autonomous test structure

Fig. 4. Probability of FC vs. autonomous test structure

#### 4. GENETIC ALGORITHM

The fitness function to be maximized with a genetic algorithm can be defines as a weighted addends being the design assessment parameters, i.e.:

- Length of testing sequence, to be maximized

- Number of ExOR gates used in SR linear feedback, to be minimized

- Number of T flip-flops within the SR structure, to be minimized.

SR will be a realization of STP structure and additional linear feedback allows its operation to be modified. The number of T flip-flops is minimized due to area overhead they carry in, since a T flip-flop can be built on the base of a simpler D flip-flop and single ExOR gate, thus realizing its feedback. Analogously, the number of ExOR gates of linear feedback is minimized because of additional area overhead necessary for implementing it.

$$f_{p} = W_{0} \cdot [d_{s}] + W_{1} \cdot [(2 \cdot (d_{r} - 1) - l_{reg, xor}) \cdot 15] + W_{2} \cdot [(d_{r} - l_{reg, T}) \cdot 45]$$

(2)

where:

$d_s$  - length of sequence,

$d_r$  - length of SR,

$l_{reg_xor}$  - max. possible number of ExOR gates of SR linear feedback,

$W_0, W_1, W_2$  - weighting coefficients, enabling significance of individual addends of the sum (2) to be modified. The constants specified under (2) provide preliminary unification for influence of individual addends of the sum (2) and enable the objective function to be replaced with a fitness function due to minimization of last two parameters.

The sampling probability  $P_r(x)$  for individual x of rank r(x) in the linear ranking selection can be computed from the following formula (3):

$$P_r(x) = a + b \left( 1 - \frac{r(x)}{r_{\max}} \right)$$

(3)

where: a, b are coefficients, r(x) – rank of individual x,  $r_{max}$  – max. rank.

Other algorithm parameters can be considered as standard. More information on genetic algorithms and its properties van be found in the work [4]

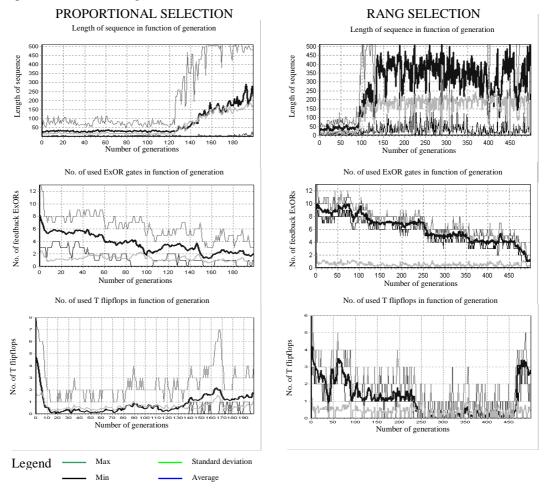

It follows from Fig. 5 that ranking selection prevails over proportional selection. The genetic algorithm that uses ranking selection finds better solutions faster and keeps stable tendency to optimizing individual parameters of fitness function (2). However, parameters a and b (3) should be chosen to exclude the worst individuals (least adapted) while maintaining appropriately large differences in probabilities  $P_r(x)$  for individuals of specified rank. It should be added that roughly comparable diagrams for both selection types was obtained only when the population for proportional selection was quadrupled compared to that of ranking selection.

Fig. 5. Proportional and Ranking selections

## 5. COMPARISON OF RESULTS

In the presented method of BIST structure design the fault coverage at the level of FC=87.98% was reached. The solutions reported in the literature [9] are listed below:

- 87.66%, ATPG approach 88.64%, 88.64% GATTO genetic system,

- 87.72% ATPG and low power, 88.64% GATTO+ genetic system,

- 88.59% CSTP structure,

- STP structure, 91.30% FSM based ATPG,

- 89.26% CA based GA,

- ed GA, -86% HITEC+BDD systems,

- 89.26% CCPS structure, 23.79% CA with 90/150 rule,

- 89.51% Selfish Gene GA, 88.64% GATTO\* genetic system.

The FC value obtained with the method presented in this paper is not the highest one compared to the solutions reported in available literature. The reached FC is of over average quality, but the presented method by using a stochastic model of digital systems considerably reduces the time of BIST structure design. For simple s298 system the simulation time is hundreds times shorter (by 308 times) than that of so far literature approach due to the BIST structure design process of specified length of testing sequence instead of time-consuming computations of FC values. The same applies to other testing systems not mentioned here.

The methods bringing the results listed above and of higher FC values were probably developed under specific approach or special heuristics were used which as dedicated methods must be better than genetic algorithm belonging to the

#### MEDICAL DEVICES AND TECHNOLOGIES

universal methods. This especially evident for Automatic Test Pattern Generation (ATPG) systems where this method focuses exclusively on selection of test vectors with no limitations related to possible implementation of the system enabling generation of such vectors, at least in the terms of area overhead. In such systems the simulation time is disadvantageously incomparable with the simulation time for the presented method and the obtained high FC value.

# 6. CONCLUSIONS

As it has been shown PRT technique does not guarantee 100% fault coverage. Some electronic and computer systems used in medicine are too significant to be tested by employing this method only. Thus, it seems be justified to supplement PRT technique with a tester possessing ability to generate deterministically specified testing sequences to detect faults uncovered by PRT. Such sequences can be defined based, for example on known gate system structure (Structural Testing) or system function (Functional Testing). Unfortunately, the use of additional testing techniques increases the design costs. The series of deterministic testing sequences can not be generated by simple tester systems but must be kept in additional memory systems, for instance in Read Only Memory (ROM) or eternal ATE testers. The testing problems mentioned above should be taken into account in tester structure design and testing procedures for digital systems used in susceptible medicine fields.

In this paper it was also shown that the application of genetic algorithm in BIST structure design is justified in the presence of a stochastic model of the tested system for PRT technique. The obtained results of simulations prove higher efficiency of ranking selection compared to proportional one in finding the best solutions, maintaining the convergence of evolutionary searching and keeping the diversity of population in consecutive generations.

## BIBLIOGRAPHY

- [1] BADURA D., Techniki projektowania samotestowalnych układów i pakietów cyfrowych wykorzystujące rejestry szeregowe z nieliniowym sprzężeniem zwrotnym, Uniwersytet Śląski, Katowice 1992 r. ISSN 0208-6336, 83-226-0449-1.

- [2] CHODACKI M., BADURA D., The Stochastic Model Pseudorandom Testing of Digital Sequential Circuits, Proceedings of XXVIII<sup>th</sup> International Autumn Colloquium ASIS 2006 Advanced Simulation of Systems, Vranov near Brno 12-14 September 2006, Czech Republic, pp. 148-151.Lp. 790.

- [3] CHODACKI M., MICHALSKI D., Genetic Algorithms Based on Stochastic Model for Pseudorandom Test Structure Design, International Carpathian Control Conference ICCC 2009, Zakopane, Poland, May 24-27, 2009.

- [4] GOLDBERG D. A., Algorytmy genetyczne i ich zastosowania, WNT 1998r., ISBN 83-204-2272-8.

- [5] HŁAWICZKA A. et al., Łatwotestowalne układy i pakiety cyfrowe, Projektowanie i testowanie, WNT Warszawa 1993r, ISBN 83-204-1518-7.

- [6] HŁAWICZKA A., Rejestry liniowe analiza, synteza i zastosowania w testowaniu układów cyfrowych, Zeszyty Naukowe Politechniki Śląskiej, Elektronika z.9 nr 1370, Gliwice 1997, ISSN 1231-1596.

- [7] KRAŚNIEWSKI A., Projektowanie samotestowanych układów cyfrowych wielkiej skali integracji, Zeszyty Naukowe Politechniki Warszawskiej, z. 83 Elektronika, 1989 r.

- [8] EDCC-2 Companion Workshop on Dependable Computing, Workshop Proceedings, Silesian Technical University, Department of Automatic Control, Electronics and Computer Science, Gliwice, May 15, 1996r., ISBN 83-906582-1-6.

- [9] http://www.cad.polito.it/FullDB/author/F.+Corno.html