# On-chip Parametric Test of R-2R Ladder Digital-to-Analog Converter and Its Efficiency

Daniel Arbet, Viera Stopjaková, Juraj Brenkuš, and Gábor Gyepes

Abstract—This paper deals with the investigation of the fault detection in separated parts of a mixed-signal integrated circuit example by implementing parametric test methods. The experimental Circuit Under Test (CUT) consisting of an 8-bit binary-weighted R-2R ladder digital-to-analog converter and additional on-chip test hardware was designed in a standard  $0.35\mu m$  CMOS technology. For detection of catastrophic and parametric faults considered in different parts of the CUT, two dedicated parametric test methods: oscillation-based test technique and  $I_{DDQ}$  monitoring were used. For the operational amplifier, on-chip and off-chip approaches have been used to compare the efficiency of both approaches in covering catastrophic faults that are hard to detect. For respective converter parts, the excelent fault coverage of 94.21% of hard-detectable faults by the proposed parametric tests was achieved.

Index Terms—Fault detection, catastrophic faults, parametric faults, on-chip parametric test, mixed-signal test

## I. INTRODUCTION

THE present trends in the development of integrated cir-**L** cuits and new advanced technologies enable integration of complex digital and mixed-signal systems on a single chip. These complex systems, know as Systems-on-Chip (SoC), can include digital, analog, and RF circuits as well as MEMS structures, microsensors and another different cores. No doubt, testability of the respective parts in such systems is greatly decreased [1]. Standard test methods cannot be straightforwardly used to test complex mixed-signal systems. Therefore, several automatic test equipments (ATE), each dedicated to a particular core integrated in the system, would be needed. Such approach increases costs of IC production unacceptably, since it requires the expensive and advanced ATE. Due to this reason, test methodology for complex systems becomes the upmost important. Test engineers have been looking for new test methods and approaches, which can assure better testability, higher fault coverage and high quality of integrated system production.

Parametric test methods are most commonly used for testing analog and mixed-signal integrated circuits (IC). These methods are based on the monitoring of a specific circuit's parameter such as voltage, supply current, frequency, etc. Evaluation of the specific parameter in a complex system is

This work was supported in part by the Ministry of Education, Science, Research and Sport of the Slovak Republic under grants VEGA 1/0285/09, VEGA 1/1008/12, VMSP-II-0042-09 APVV and the "Centre of Excellence for Smart Technology, Systems and Services II", ITMS Code 26240120005.

All authors are with Institute of Electronics and Photonics, Faculty of Electrical Engineering and Information Technology, Slovak University of Technology, Ilkovicova 3, Bratislava 812 19, Slovakia (corresponding author: D. Arbet, phone: +421260291163; fax: ++421265423480; e-mail: daniel.arbet@stuba.sk).

difficult because it requires sophisticated sensing and analyses of the selected parameter in terms of additional hardware needed, setting the Pass/Fail limit, robustness, etc. (in comparison to the simple logic test). On the other hand, parametric test, performed for a part of the complex system, may be the only proper and/or implementable test approach in some applications [2]. Such approach is based on dividing the complex system into smaller parts that could be easily tested separately, each part by a dedicated test method.

In this paper, an 8-bit R-2R ladder digital-to-analog converter (DAC) was used as the test vehicle. Considering the structure of this circuit, it was split into two parts, which have been tested separately using two different parametric test methods. Thus, the control logic, used for selecting the test method and switching the circuit mode (test/functional), has been designed. In Section 2, the preliminary work done in the respective area is described. Experimental CUT is presented in more details in Section 3. In Section 4, the proposed test strategies employed in test of the respective part of the DAC are described. In Section 5, influence of additional test hardware on the DAC preformance is addressed. Simulation results and achieved fault coverage are summarized in Section 6. In the last section, the efficiency of the proposed test method through the obtained experimental results is discussed.

# II. PRELIMINARY WORK

Digital-to-analog converters and analog-to-digital converters (ADC) are very often used circuits in the mixed-signal integrated systems. However, to test such systems by conventional external approaches, accurate measurement instruments as well as advanced and costly ATE [3] are necessary. Therefore, Built-In Self Test (BIST) approaches represent the best solution or sometimes, even the only possible way of testing mixed-signal circuits like converters are. Thus, BIST can significantly reduce test time and overall cost since the most difficult tasks are performed directly on a chip.

In the last years, many BIST structures have been published, and several different modifications of BIST approach applicable to DAC and ADC have been proposed [4]–[6]. The IEEE standard for terminology and test methods of digital-to-analog converters is described in [7]. In [8]–[10], different on-chip test hardware has been proposed and used for testing the data converters. BIST metodologies using different on-chip input stimuli generators were described in [11] and [12]. A BIST scheme for DAC testing, based on the undersampling technique presented in [13], was proposed in [14]. The oscillation-based test for analog-to-digital and digital-to-analog converters has been addressed in [6], [15] and [16].

Another BIST structures for very popular R-2R ladder DAC were addressed in [9], [17].

However, the efficiency of the existing on-chip test approaches in covering real hard-detactable faults has still some limitations, and it shoud be improved in order to assure the necessary reliability. Moreover, most of the parametric test methods are not mature enough to be implemented as fully on-chip test approach, since they suffer either from complexity of the hardware or from test stimuli gereration.

In this paper, on-chip parametric test of 8-bit R-2R ladder DAC is presented. The converter is split into two parts: the operational amplifier and R-2R resistor network, which are tested separately by oscillation test method [18]–[21] and  $I_{DDQ}$  monitoring [22]–[25], respectively. This approach is easy to implement and offers rather high fault coverage of hard-detectable faults. Furthermore, input test stimuli are easy to generate on-chip, and the proposed approach is able to identify a defective part of the CUT.

## III. EXPERIMENTAL CIRCUIT UNDER TEST

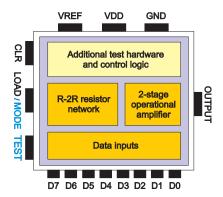

Fig. 1 shows the block diagram of the experimental mixed-signal circuit designed in  $0.35\mu m$  CMOS technology, which consists of the selected converter and the necessary on-chip test hardware, including the control logic used for switching the circuit into the test mode. As a mixed-signal CUT, an 8-bit binary-weighted R-2R ladder DAC have been designed and used in our experiment. In the test mode, the DAC circuit is split into two separated parts: a 2-stage operational amplifier (OPAMP) and the R-2R resistor network. Using two additional inputs TEST and MODE, the circuit can be switched in one of two test modes in order to test the respective part of the converter separately, each by employing a dedicated parametric test method.

Fig. 1. Block diagram of the mixed-signal CUT used

#### IV. PROPOSED TEST STRATEGY

# A. Off-chip test of operational amplifier

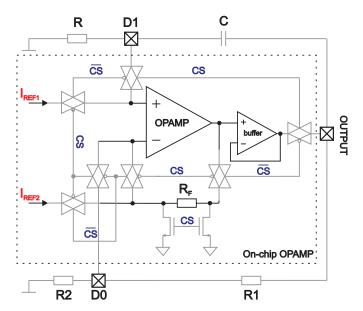

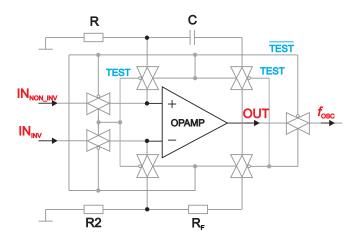

For the fault detection in the operational amplifier (OPAMP), the oscillation test method transforming the amplifier into an oscillator by inserting a feedback RC network was used. Using this method, different faults present in the amplifier and causing deviation either in the oscillation frequency or

Fig. 2. Circuit diagram of the OPAMP circuit transformed into an oscillator (without control logic)

in the amplitude of oscillations (exceeding the nominal fault-free tolerance range) can be detected [20].

Components in the feedback network were connected externally (by T-gates) using two additional input pins (DO and D1) and the output pin OUTPUT (Fig. 2). In this configuration, a smaller deviation in the oscillation frequency and the amplitude of oscillations were reached. The feedback resistor  $R_F$ , which is a part of the DAC, is clamped to ground using two MOS transistors. A buffer is a default part of the converter but in this topology, it was also used to separate the OPAMP from possible external influences. The OPAMP can be tested by applying logic 1 and logic 0 to pins TEST and MODE, respectively (Fig. 1). Then the common control logic (not depicted in Fig. 2) generates the control signals (CS) for T-gates that for test purposes, disconnect the OPAMP from the R-2R resistor network and connect the feedback network.

T-gates were used for insertion of the feedback. However, they may cause the CUT performance degradation and therefore, their ON- and OFF- resistances must be as low as possible and as high as possible, respectively. Hence, the ON-resistance of T-gates, which are appearing in the signal path, must be minimized to prevent the undesired performance degradation [26].

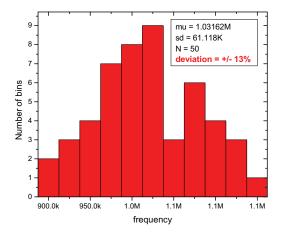

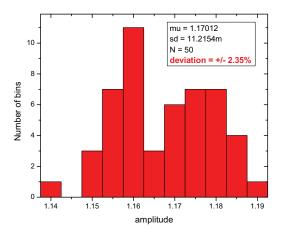

The fault-free tolerance bands (representing process variations and temperature influence) for the oscillation frequency and the amplitude of the oscillation frequency were obtained by Monte Carlo analysis, and are depicted in Fig. 3 and Fig. 4, respectively. Deviations (obtained by 50 runs) of  $\pm 13\%$  in the oscillation frequency and of  $\pm 2.85\%$  in the oscillation amplitude were observed.

# B. On-chip test of operational amplifier

Previously, the feedback network and passive components were realized externally using discrete devices in order to achieve higher accuracy and smaller deviation in the oscillation

Fig. 3. Nominal deviation in the oscillation frequency

Fig. 4. Fault-free deviation in the amplitude of oscillations

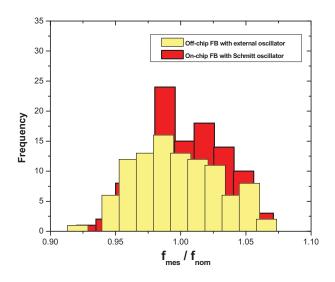

frequency and the amplitude of oscillations. Taking into account SoC testing requirements, where a sort of BIST strategy to test the mixed-signal cores (e.g. DACs) is demanded, an on-chip test should be performed. Therefore, in such case, the OPAMP feedback network must be connected internally, using devices with about 20% deviation in technology parameters. In [21], such OBIST strategy for testing OPAMP as a part of complex analog and mixed-signal systems is described. To evaluate the efficiency of this test strategy, the circuit oscillation frequency is then compared to the reference frequency given by a Schmitt trigger oscillator, which was used as the on-chip frequence reference to compensate technology variations. Fig. 5 shows the circuit diagram of the on-chip oscillator using an on-chip feedback network for transforming the OPAMP into the oscillator.

The oscillation frequency was evaluated by countering a number of oscillation pulses exhibited by the CUT during a time interval generated by the reference oscillator. Influence of technology variations on the oscillation frequency for fault-free CUT was obtained from Monte Carlo analysis. MC analysis of technology variations of  $\pm 3\sigma$  was performed for all devices used in the CUT and additional test hardware. To demonstrate the efficiency of the on-chip oscillation test approach, the fault-free tolerance bands obtained for the on-chip feedback network realization was compared to the one

Fig. 5. Circuit diagram of the OPAMP circuit transformed into an oscillator (without control logic)

obtained for external reference oscillator (Fig. 6).

Fig. 6. Comparison of the oscillation frequency tolerance bands for on-chip and off-chip reference oscillator solutions

From Fig. 6, one can observe that deviation in the oscillation frequency for the on-chip feedback network and the on-chip reference oscillator is pretty much the same as the oscillation frequency deviation obtained by off-chip feedback network and the external oscillator. This result proves that the oscillation test strategy offers the on-chip test of the operational amplifier as a separated part of the experimental DAC. With the on-chip test, standard mixed-signal SoC test requirements could be fulfilled. A more detailed description of the proposed on-chip test strategy, including the oscillation frequency evaluation and the PASS/FAIL threshold selection, is presented in [21].

## C. Test of R-2R resistor network

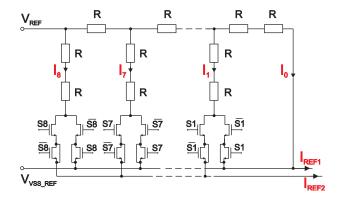

The R-2R ladder is a resistor network that uses a cascaded structure of current dividers, which generate binary-weighted currents in the respective branches, as shown in Fig. 7. In ideal

Fig. 7. Circuit diagram of the R-2R ladder

case, the dividing ratio should be 2:1 but because of resistors mismatch, in reality, the divisions will be imperfect.

The most probable fault in the resistor ladder is that the value of a resistor exceeds its tolerance band (parametric fault). These faults can be detected by the measurement and evaluation of current value in the respective current branches. The described technique has been used for parametric test of the R-2R ladder, which represent a substantial part of the whole DAC circuit. Modification of this method, used in digital IC test, is known as  $I_{DDQ}$  testing.

Principle of current testing of the R-2R ladder is as follows: in the first step, current I8 is compared to the sum of currents I7 to I0, then in the second step, the control logic turns-off switches S8 and  $\overline{S8}$ , and current I7 is compared to the sum of currents I6 to I0. Consequently, control logic turns-off switches S7 and  $\overline{S7}$ , and another two currents are compared.

This procedure goes on till the last two current branches are processed.

The current difference at each step of the proposed test procedure can be expressed as follows:

$$I_{diff\_N} = I_N - \left(\sum_{i=0}^{N} I_{N-1}\right)$$

(1)

where N = 1, 2, 3, ... 8 and IN is current in the respective branch being sensed.

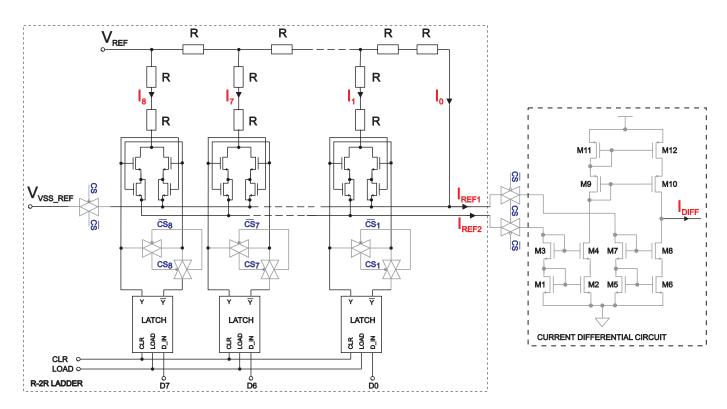

Circuit diagram of R-2R ladder with the additional test hardware is depicted in Fig. 8. In every branch of the resistive network, two T-gates were included to switch-off the corresponding branch. Control signals for T-gates (CS,  $\overline{CS}$  and also  $CS_1$  -  $CS_8$ ) were generated by the common control logic. Circuitry performing the current difference consists of three cascode current mirrors, as shown in Fig. 8 (right side). This circuit also ensures that the differential current (difference of  $I_{REF1}$  and  $I_{REF2}$ ) will flow out to the circuit's output.

This approach can test the resistor ladder in total eight steps, by shifting the logic 1 from MBS to LSB. The main problem of this method is that current in the last branch is in order of nA, which is difficult to sense and measure with necessary precision. Therefore, this test technique might be limited to ladders that use resistors with the resistance value smaller than  $10\mathrm{k}\Omega$ . A fault-free tolerance band of the differential current  $I_{diff}$  was obtained by Monte Carlo analysis and achieved results will be presented in the following section.

Fig. 8. Circuit diagram of R-2R ladder with additional test hardware (without control logic)

# V. INFLUENCE OF ADDITIONAL TEST HARDWARE

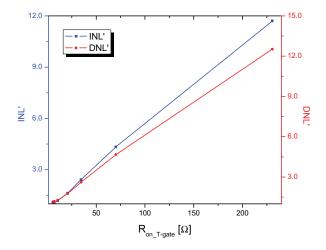

Insertion of the necessary on-chip test hardware might undesirably affect the DAC performance. The main reason is probably the use of T-gates (disconnecting the individual parts), which have some resistance in switch-on state. The most critical are T-gates that are connected in the path leading to the circuit output. Fig. 9 shows how the integral and the differential nonlinearity (INL' and DNL') of the DAC (with the test hardware) depend on the ON resistance of T-gates connected in the path leading to the converter output.

Fig. 9. INL' and DNL' versus  $R_{ON}$  of T-gate

It can be observed that in order to maintain the original parameters of DAC,  $R_{ON}$  of T-gates should be order of tens of Ohms. If the T-gates with  $R_{ON}$  of about 10  $\Omega$  are used, the value of integral and differential nonlinearity will be increased by 18% and 27%, respectively. In such case, the additional test hardware will require the area of 0.002  $mm^2$ , which means that the total area will be enlarged by 13%. From the aspect of testing it is therefore, necessary to find a good compromise between the CUT performance and the test hardware area overhead.

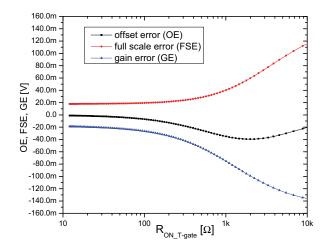

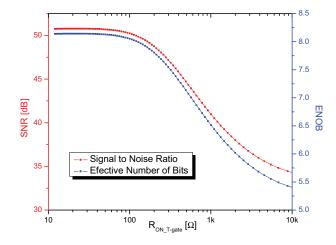

Fig. 10 and Fig. 11 show how the other main parameters of the digital-to-analog converter (with the additional test hard-

Fig. 10. OE, FSE and GE versus  $R_{ON}$  of T-gate

Fig. 11. SNR and ENOB versus  $R_{ON}$  of T-gate

ware) depend on the switch-on resistance of T-gates connected in path leading to the converter output.

It can be observed that to maintain the original value of the full scale error (FSE), signal-to-noise ration (SNR) and effective number of bits (ENOB) parameters, it would be sufficient to use T-gate with  $R_{ON}$  of about  $100~\Omega$ . However, achieve the original values of INL, DNL, offset error (OE) and gain error (GE),  $R_{ON}$  should be about of tens of Ohms. Thus, it can be concluded that to maintain the original value of all parameters of the converter,  $R_{ON}$  of T-gates should be kept in the range from 10 to 100 Ohms. In this case, the total area overhead would be enlarged from 6.5% to 13%.

## VI. ACHIEVED RESULTS

For verification of the efficiency of the proposed test methods in testing parts of DACs, four types of catastrophic faults in the OPAMP, and two parametric faults in the R-2R ladder were considered. Catastrophic faults such as shorts, opens, gate-oxide shorts (GOS) and floating gates (FG) were inserted. Short and open faults were injected in all connection paths, while GOS and FG faults were applied in all transistors forming the OPAMP. Parametric faults, which most commonly arise on passive devices, were modeled and injected in the R-2R resistor network.

# A. Results of the operational amplifier test

In the operational amplifier, several catastrophic faults such as opens and shorts as well as floating gates and gate-oxide-shorts, were considered. For their detection, the oscillation-based test method of the OPAMP circuit was employed.

Opens were modeled using a parallel combination of a resistor and a capacitor. Resistors and capacitors values depend on the defect location and size. We have considered nine different open faults injected in 24 different locations. From all considered 216 opens, 209 faults were detected, which means that the fault coverage of 94% was achieved. However, opens modeled with the resistance value of 1 M $\Omega$  represent so call hard-detectable faults. Thus, opens having higher resistance would probably not be covered by other test technique either.

Short faults were modeled and simulated using a serial short resistor. Values of resistors considered as short faults are as follows: 500  $\Omega$ , 1k  $\Omega$ , 10k  $\Omega$ , 100 k $\Omega$  and 1 M $\Omega$ . The achieved fault coverage, presented for different ranges of the short resistance value, is presented in Table I.

TABLE I

FAULT COVERAGE OF SHORT FAULTS

| $\mathbf{R_{short}} [\Omega]$ | 500 ÷ 10k | 500 ÷ 100k | 500 ÷ 1M |

|-------------------------------|-----------|------------|----------|

| Fault Coverage                | 100%      | 95.58%     | 84.7%    |

It can be observed that shorts with lower resistance are easier to detect because, in most cases, such shorts lead to loss of the oscillations or significant deviation in the amplitude of oscillations. Shorts with the resistance higher than 100 k $\Omega$  usually cause only slight deviation in the oscillation frequency that makes them more difficult to detect.

For floating gates (FG) we used an extended electrical model described in [27], considering also capacity of the break. Hence, the FG fault model includes capacitors  $C_{mp}$ ,  $C_{pb}$  and  $C_{break}$ , which values were set to 2.82 fF, 3.02 fF and 0.07 fF, respectively. All considered FG faults were easily detected through either loss of the oscillation or a change in the oscillation frequency (single fault). The worst case of the overall fault coverage of all catastrophic faults, using the external oscillator feedback network, is summarized in Table II.

TABLE II

WORST CASE OF OFF-CHIP TOTAL FAULT COVERAGE

| Faults | Fault coverage |  |

|--------|----------------|--|

| Shorts | 84.7%          |  |

| Opens  | 94%            |  |

| FGs    | 100%           |  |

| Total  | 92.9%          |  |

The total fault coverage achieved for on-chip realization of the proposed parametric test of the OPAMP block is summarized in Table III.

| Faults | inserted | detected | Fault coverage |

|--------|----------|----------|----------------|

| Shorts | 68       | 54       | 79.41%         |

| Opens  | 216      | 180      | 83.33%         |

| FGs    | 9        | 7        | 77.77%         |

| Total  | 293      | 241      | 82.25%         |

The off-chip approach offers slightly higher total fault coverage than the one achieved in case of on-chip test realization. On the other hand, on-chip approach enables a BIST that is typical for SoC testing. However, some of the undetected faults have been manifested by a certain deviation in the amplitude of oscillations (not evaluated in our experiment). Therefore, the total fault coverage might be increased further by evaluation of this parameter. The obtained results prove that the oscillation-based test approach can be relatively very efficient in detecting

different catastrophic faults (including hard-detectable ones) in analog sub-circuits.

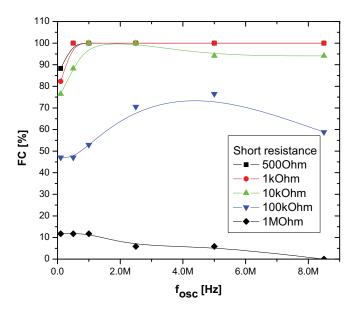

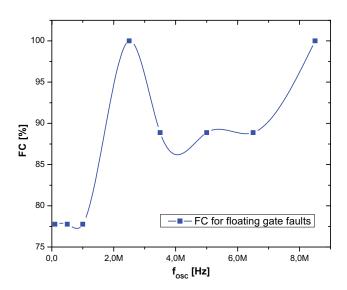

We also analyzed the possible dependence of the fault coverage in the OPAMP on the value of the oscillation frequency. To test the amplifier by oscillation-based strategy at different oscillation frequencies, the value of passive devices used in the positive feedback loop was varied. The fault coverage dependence on the value of the oscillation frequency for different shorts and floating gates is shown in Fig. 12 and Fig. 13, respectively.

Fig. 12. Fault coverage versus the value of the oscillation frequency for different shorts

One can observe that the best fault coverage can be achieved at the oscillation frequency of about 2 MHz. Shorts with lower resistance are easy to detect since they usually cause loss of oscillations. Shorts with higher resistance (e.g. of 100 k $\Omega$ , 1 M $\Omega$ ) cause deviation from the oscillating frequency, which

Fig. 13. Fault coverage versus the oscillation frequency value for floating gate faults

makes them more difficult to detect. Generally, the shorts with lower short resistance are easily detectable at lower oscillation frequencies, while the shorts with higher resistance (in order of 100 k $\Omega$ ) are better covered at the higher frequency (about 4.5 MHz). Finally, shorts with resistance of 1 M $\Omega$  have lowest fault coverage in whole frequency range but those faults have a low probability of presence.

Secondly, the fault coverage dependence on the value of the oscillation frequency for floating gate faults was investigated (Fig. 13). It can be observed that 100% fault coverage can be achieved for the value of the oscillation frequency of 3 MHz and also for values higher than 8 MHz. Unfortunately, for the frequency higher than 8.5 MHz the CUT does not fulfill the conditions needed for the appearance of sustained oscillations.

# B. Results of R-2R ladder test

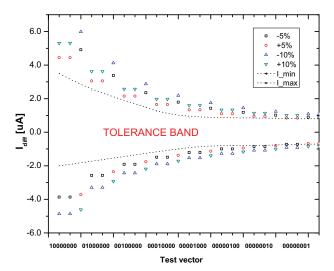

In contrast to the OPAMP test, parametric faults were considered in the resistor network (R-2R ladder), and the fault coverage by the proposed current test method was investigated. Possible parametric faults in the resistor network were simulated using a resistor with varying its resistance value. It was considered that the value deviates by 5% or 10% from the tolerance range. Fig. 14 shows the tolerance band and simulated values of the output differential current depending on the test vector being applied.

Fig. 14. Tolerance band and simulated values of the differential current in R-2R ladder

The simulation results show that almost all parametric faults in the resistor network are detectable. However, parametric fault considered in the last branch is difficult to detect because the current is too small to be sensed precisely. Table IV shows the fault coverage achieved by current monitoring approach for parametric faults considered in the resistor network. It can be observed that 10% deviation in resistors value is fully detectable and 100% fault coverage is reached. When the resistors value deviates from its tolerance band by 5%, the fault coverage is slightly lowered to 96% that is still very good result.

Finally, we can state that the proposed current test method is easy to implement and provides very high efficiency in

TABLE IV FAULT COVERAGE OF SHORT FAULTS

| Parametric fault | ±5% deviation | ±10% deviation |

|------------------|---------------|----------------|

| Fault Coverage   | 96%           | 100%           |

covering parametric faults. However, the method might be limited by resistance values of resistors used in the ladder, since high values lead to less current flowing through the respective branches, which is rather difficult to be measured and processed.

#### VII. DISCUSSION & CONCLUSION

Two different parametric test methods have been used for on-chip fault detection in the R-2R ladder digital-to-analog converter. For this purpose, an experimental circuit, consisting of the DAC, the additional test hardware, and the control logic for switching the DAC between functional and test modes, has been designed in selected CMOS technology. The control logic was used to split the circuit into two parts, each tested separately by a dedicated method. An operational amplifier was tested by the oscillation-based test strategy, while current monitoring was used to test the resistor ladder. The crucial point of the used test strategy is that the insertion of the necessary additional test hardware might affect the CUT performance. However, with appropriate setting of  $R_{ON}$  of the inserted T-gates, this influence can be minimized. T-gates with  $R_{ON}$  of about 10  $\Omega$  cause area overhead of 13%, and increase of 18% and 27% in INL and DNL parameters, respectively. Catastrophic and parametric faults were considered in the CUT. In the worst case, the total fault coverage of 92.42% and 96% for the OPAMP and the resistor network was achieved, respectively. This is an excellent result especially, if taking into account that the fault coverage up to 94.21% of harddetectable faults by parametric test of single parts of the DAC has been achieved. The on-chip total fault coverage might be increased by measuring the amplitude of oscillation. However, for evaluation of the amplitude of oscillation, the additional test hardware will be necessary, which would increase the area overhead.

On-chip parametric test of separated parts is a promising strategy to test complex mixed-signal systems. This approach offers the possibility to identify a defective part and makes test of such systems easier or, in some applications, even possible at all. However, it is necessary to maintain the circuit's original functionality and specific parameters. Further research in this field will be focused on realization of BIST structures, based on the oscillation test strategy, which would be generally applicable for digital-to-analog converters as cores used in complex SoCs.

#### ACKNOWLEDGMENT

This work was supported in part by the Ministry of Education, Science, Research and Sport of the Slovak Republic under grants VEGA 1/0285/09, VEGA 1/1008/12, VMSP-II-0042-09 APVV and the "Centre of Excellence for Smart Technology, Systems and Services II", ITMS Code 26240120005. Authors also thank R-DAS, s.r.o for research support.

#### REFERENCES

- [1] T. Jeng-Horng, M.-J. Hsiao, and T.-Y. Chang, "An embedded built-inself-test approach for digital-to-analog converters," in *Test Symposium*, 2001. Proceedings. 10th Asian, 2001, pp. 423 –428.

- [2] M. H., "Test requirements for todays and future circuits: A perspective," in *Proceedings of Electronic circuits and Systems*, 2005, pp. 1 –10.

- [3] J. L. H. Diaz, Test and Design-for-Testability in Mixed-Signal Integrated Circuits, 1st ed. Springer, October 2004, no. 1402077246.

- [4] J. Wibbenmeyer and C.-I. Chen, "Built-in self-test for low-voltage high-speed analog-to-digital converters," *Instrumentation and Measurement, IEEE Transactions on*, vol. 56, no. 6, pp. 2748 –2756, dec. 2007.

- [5] H. Xing, H. Jiang, D. Chen, and R. Geiger, "High-resolution ADC linearity testing using a fully digital-compatible BIST strategy," *Instrumentation and Measurement, IEEE Transactions on*, vol. 58, no. 8, pp. 2697 –2705, aug. 2009.

- [6] K. Arabi, I. Kaminska, and J. Rzeszut, "BIST for D/A and A/D converters," *Design Test of Computers, IEEE*, vol. 13, no. 4, pp. 40 –49, winter 1996.

- [7] "IEEE draft standard for terminology and test methods of digital-toanalog converter devices," *IEEE P1658/D8.8*, *June 2011*, pp. 1 –127, 28 2011

- [8] K. Arabi, B. Kaminska, and M. Sawan, "On chip testing data converters using static parameters," *Very Large Scale Integration (VLSI) Systems*, *IEEE Transactions on*, vol. 6, no. 3, pp. 409 –419, sept. 1998.

- [9] J. Ramesh, M. Srinivasulu, and K. Gunavathi, "A novel on chip circuit for fault detection in digital to analog converters," in *Control, Automa*tion, Communication and Energy Conservation, 2009. INCACEC 2009. 2009 International Conference on, june 2009, pp. 1 –8.

- [10] J.-L. Huang, C.-K. Ong, and K.-T. Cheng, "A BIST scheme for onchip ADC and DAC testing," in *Design, Automation and Test in Europe* Conference and Exhibition 2000. Proceedings, 2000, pp. 216 –220.

- [11] K. Arabi, B. Kaminska, and J. Rzeszut, "A new built-in self-test approach for digital-to-analog and analog-to-digital converters," in Computer-Aided Design, 1994., IEEE/ACM International Conference on, nov 1994, pp. 491 –494.

- [12] E. Teraoka, T. Kengaku, I. Yasui, K. Ishikawa, T. Matsuo, H. Wakada, N. Sakashita, Y. Shimazu, and T. Tokuda, "A built-in self-test for ADC and DAC in a single-chip speech CODEC," in *Test Conference*, 1993. Proceedings., International, oct 1993, pp. 791 –796.

- [13] C. W. Lin, S. F. Lin, and S. F. Luo, "A new approach for nonlinearity test of high speed DAC," in *Mixed-Signals, Sensors, and Systems Test Workshop*, 2008. IMS3TW 2008. IEEE 14th International, june 2008, pp. 1 –5.

- [14] C. W. Lin and S. F. Lin, "A BIST scheme for testing DAC," in Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), 2012 9th International Conference on, may 2012, pp. 1 –4.

- [15] B. Kaminska and K. Arabi, "Mixed signal DFT: a concise overview," in Computer Aided Design, 2003. ICCAD-2003. International Conference on, nov. 2003, pp. 672 – 679.

- [16] E. J. Peralas, A. Rueda, and J. L. Huertas, "New BIST schemes for structural testing of pipelined analog to digital converters," *Journal of Electronic Testing*, vol. 17, pp. 373–383, 2001, 10.1023/A:1012747017838. [Online]. Available: http://dx.doi.org/10.1023/A:1012747017838

- [17] Y. Jun and T. Masayoshi, "A BIST scheme based on resistance match for current-mode R-2R ladder digital-to-analog converter," in *Computer Research and Development (ICCRD)*, 2011 3rd International Conference on, vol. 3, march 2011, pp. 305 –309.

- [18] K. Arabi and B. Kaminska, "Parametric and catastrophic fault coverage of analog circuits in oscillation-test methodology," in VLSI Test Symposium, 1997., 15th IEEE, apr-1 may 1997, pp. 166 –171.

- [19] G. H. Sanchez, V. G. D. L. V. Diego, and R. Adoracisn, Oscillation-Based Test in Mixed-Signal Circuits (Frontiers in Electronic Testing). Secaucus, NJ, USA: Springer-Verlag New York, Inc., 2006.

- [20] K. Arabi and B. Kaminska, "Oscillation-test strategy for analog and mixed-signal integrated circuits," in VLSI Test Symposium, 1996., Proceedings of 14th, apr-1 may 1996, pp. 476 –482.

- [21] D. Arbet, J. Brenkus, G. Gyepes, and V. Stopjakova, "Increasing the efficiency of analog OBIST using on-chip compensation of technology variations," in *Design and Diagnostics of Electronic Circuits Systems* (DDECS), 2011 IEEE 14th International Symposium on, april 2011, pp. 71 –74

- [22] R. Rajsuman, "Iddq testing for CMOS VLSI," *Proceedings of the IEEE*, vol. 88, no. 4, pp. 544 –568, april 2000.

- [23] S. Bhunia, H. Li, and K. Roy, "A high performance IDDQ testable cache for scaled CMOS technologies," in *Test Symposium*, 2002. (ATS '02). Proceedings of the 11th Asian, nov. 2002, pp. 157 – 162.

- [24] R. Rajsuman, "Design-for-iddq-testing for embedded cores based system-on-a-chip," in *IDDQ Testing*, 1998. Proceedings. 1998 IEEE International Workshop on, nov 1998, pp. 69 –73.

- [25] V. Stopjakova and H. Manhaeve, "CCII+ current conveyor based BIC monitor for IDDQ testing of complex CMOS circuits," in *European Design and Test Conference*, 1997. ED TC 97. Proceedings, mar 1997, pp. 266 –270.

- [26] K. Arabi and B. Kaminska, "Oscillation built-in self test (OBIST) scheme for functional and structural testing of analog and mixed-signal integrated circuits," in *Test Conference*, 1997. Proceedings., International, nov 1997, pp. 786 –795.

- [27] A. M. Brosa and J. Figueras, "Characterization of floating gate defects in analog cells," *Journal of Electronic Testing*, vol. 14, pp. 23–31, 1999, 10.1023/A:1008388903741. [Online]. Available: http://dx.doi.org/10.1023/A:1008388903741

Daniel Arbet received the M.S. degree in Electronics from Slovak University of Technology in Bratislava, Slovakia in 2009. Since October 2009 he has been a PhD student at the Institute of Electronics and Photonics of Slovak University of Technology. He has published more than 10 papers. His main research interests are low-voltage low-power analog design, on-chip parametric testing, analog BIST and test implementation.

Viera Stopjaková received the M.S. degree and the PhD degree in Electronics from Slovak University of Technology in Bratislava, Slovakia, in 1992, and 1997, respectively. From October 1997 to September 2003 and from October 2003 to June 2009 she was an assistant professor and an associated professor at Microelectronics Department, Faculty of Electrical Engineering and Information Technology of Slovak University of Technology in Bratislava, respectively. Currently, she is a full professor at the Institute of Electronics and Photonics of the same university.

She has been involved in several EU funded research projects under different funding schemes such as TEMPUS, ESPRIT, Copernicus, FP, ENIAC-JU, and also in national research grants. She has published over 90 papers in various journals and conference proceedings; and she is a co-inventor of two US patents in the field of on-chip supply current testing. Her main research interests include IC design, VLSI & SoC testing, on-chip testing, design and test of mixed-signal circuits, biomedical monitoring, and neural network implementations and applications.

Juraj Brenkuš received the M.S. degree in Electronics from Slovak University of Technology in Bratislava, Slovakia in 2000. Since March 2010 he has been a researcher at Institute of Electronics and Photonics of Slovak University of Technology. He is the author or co-author of more than 20 papers presented at international conferences. His main research interests are IC design and test, mixed-signal systems design, SoC design, on-chip testing and test development automation.

Gábor Gyepes received the M.S. degree in Electronics from Slovak University of Technology in Bratislava, Slovakia in 2009. Since October 2009 he has been a PhD student at the Institute of Electronics and Photonics of Slovak University of Technology. His main research interests include analog IC design, memory test and on-chip current testing. He has published more than 10 papers in these areas.