# Modeling the Characteristics of a High-*k* HfO<sub>2</sub>-Ta<sub>2</sub>O<sub>5</sub> Capacitor in Verilog-A

George V. Angelov, Member, IEEE

Abstract—A circuit simulation model of a MOS capacitor with high-k HfO<sub>2</sub>–Ta<sub>2</sub>O<sub>5</sub> mixed layer is developed and coded in Verilog-A hardware description language. Model equations are based on the BSIM3v3 model core. Capacitance-voltage (C–V) and current-voltage (I–V) characteristics are simulated in Spectre circuit simulator within Cadence CAD system and validated against experimental measurements of the HfO<sub>2</sub>–Ta<sub>2</sub>O<sub>5</sub> stack structure.

Index Terms—Device modeling, compact models, circuit simulation, high-k gate dielectric, Verilog-A, Spectre

#### I. INTRODUCTION

DEVICE modeling is a key milestone to efficiently achieving the analog design objectives. The demand for efficient circuit simulation models is increasing due to two ongoing developments: the technology scaling into nanoregime and system integration with many different functions on a single chip [1]. The linear scaling of classical bulk Si CMOS transistors approaches its physical limits and it will be possible in the future only if new materials are introduced in CMOS device structures or if new device architectures are implemented. Innovations in the electronics industry have been possible because of the strong correlation between devices and materials research [2]. The requirement for low voltage, low power and high performance are the major challenges for the engineering of sub-32-nm gate length CMOS devices [3].

To maintain a proper control of the drain current flow in nanoscale CMOS devices, the thickness of SiO<sub>2</sub>, which is the conventional gate dielectric material in the last four decades, is now pushed towards its technological limit of 1 nm and theoretical limit of about 0.7 nm. Further device downsizing following Moore's law would require even thinner gate dielectric films [4], [5]. This can only be achieved by using materials with high dielectric constant (high-k) to replace the conventional SiO<sub>2</sub>. The introduction of high-k materials resolves the constraint of downsizing the oxide thickness and has been recognized as an effective technological option to boost the performance of state-of-the-art integrated circuit technology. The emerging nanoelectronic transistors will rely on non-silicon high-k gate materials with target effective oxide thickness (EOT) of less than 1 nm (in the 65 nm technology

This work was supported by Contract No. UNIK DUNK - 01/03.12.2009. G. V. Angelov, PhD, assistant professor, is with the Technical University of Sofia, FETT, Dept. of Microelectronics, ECAD Laboratory, phone +359 2 965 3115, fax +359 2 965 2330, (e-mail: gva@ecad.tu-sofia.bg).

node with channel length of 32 nm, the thickness of  $SiO_2$  is  $\approx$  0.9 nm) to advance beyond the sub-32-nm regime [2], [4], [6].

By using dielectric with higher k value, a larger value of gate capacitance can be achieved with a physically thicker film. With reference to the same capacitance value as implemented using silicon dioxide, the effective thickness of high-k dielectric film is reduced by a factor of  $k_{ox}/k_{\text{high-}k}$  (where  $k_{ox}$  and  $k_{\text{high-}k}$  are the dielectric constant of silicon oxide and high-k material, respectively). That is the idea of equivalent oxide thickness (EOT) which is defined as:

$$EOT = \frac{k_{ox}}{k_{high-k}} t_{high-k}$$

where  $t_{high-k}$  is the physical thickness of high-k dielectric material.

There are many alternative high-*k* materials being investigated. Most promising candidates are the multicomponent gate dielectrics based on a variety of metal oxides; ionic metal oxides, having highly polarized metal-oxygen bonds, would have even larger *k* values than the covalent dielectric materials. To date, Ta<sub>2</sub>O<sub>5</sub> is one of the best high-*k* dielectric candidates for storage capacitors of nanoscale dynamic random access memories (DRAMs) while HfO<sub>2</sub> appears to be the respective candidate for nano-MOSFETs [6], [7], [8]. Hf-based materials, such hafnium silicates and hafnium aluminates, have been considered as the most promising materials and have already been used in the state-of-the-art CMOS technology. An example for the benefit of using high-*k* material is the Intel Core 2 family of processors fabricated by 45 nm hafnium-based CMOS technology.

To assist technology development the most important modeling issue is to ensure sufficient simulation accuracy and applicability for any technology. For achieving this task it is essential to maintain a physically correct modeling of the real technological origins of the effects in new device structures.

Compact device models are usually coded in circuit simulators using general-purpose languages. Accordingly, they are targeted specifically to the interface and internal data structures of their host simulator, and hence are inherently non-portable. In this context modification and optimization of a given model becomes a time-consuming and error-prone task. An effective approach to overcome this gap between model development and its subsequent implementation in CAD tools is to formulate open source code models in analog

hardware description languages (HDLs) such as Verilog-A/AMS or VHDL-AMS. In the recent years Verilog-A has become increasingly viewed as efficient instrument for compact modeling purposes [9].

This paper presents a compact model for circuit simulation of the high-k MOS capacitor with  $HfO_2$ – $Ta_2O_5$  mixed layer structure from [10]. The electrical characteristics prove that the multicomponent structure composed of  $HfO_2$ – $Ta_2O_5$  mixed layer deposited on Si performs as high-k layer in terms of permittivity, allowable level of leakage current, and appropriate oxide interface properties [10]. The compact model is coded in Verilog-A HDL based on the BSIM3v3 model equations. Capacitance-voltage (C–V) and current-voltage (I–V) characteristics are compared to the measurements to validate the model.

### II. DEVICE FABRICATION AND CHARACTERIZATION

The modeled MOS capacitor structures are fabricated on chemically cleaned p-type (100) 15  $\Omega$ cm Si wafers used as substrates. The HfO<sub>2</sub> layer with two thicknesses of 5 and 7 nm is deposited by RF sputtering of Hf target in Ar + 10% O<sub>2</sub> atmosphere on top of RF sputtered Ta<sub>2</sub>O<sub>5</sub> with the same thicknesses. The wafer temperature is maintained at 200 °C during the deposition of the two types of films; the working gas pressure is 0.33 Pa and RF power density is 3.6 W/cm<sup>2</sup>; Ta and Hf targets both with a purity of 99.99 % are used. The total film thickness, d and the refractive index, n are measured by ellipsometry ( $\lambda = 632.8$  nm); the physical thickness of the stacked films is 10 and 15 nm. Relatively large layer thicknesses are intentionally used in order to minimize the very small thickness-related effects and to study the effect of layers intermixing itself. According to X-ray diffraction analysis both types of films the pure Ta<sub>2</sub>O<sub>5</sub> and the HfO<sub>2</sub>- $Ta_2O_5$  are amorphous [10].

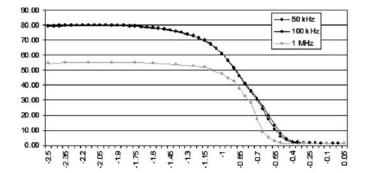

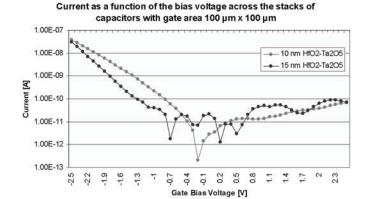

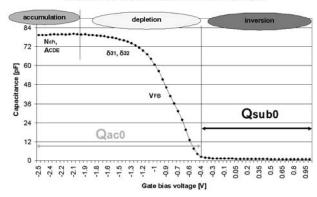

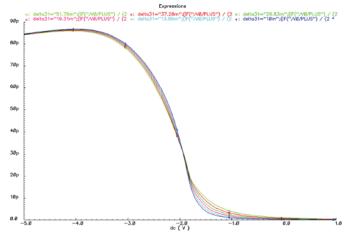

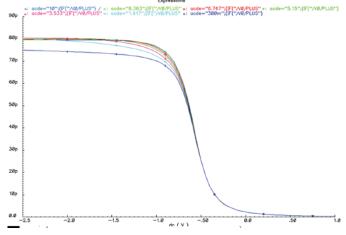

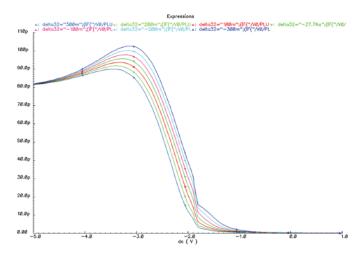

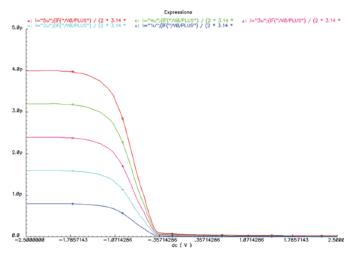

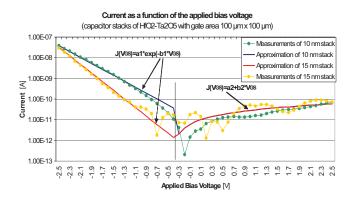

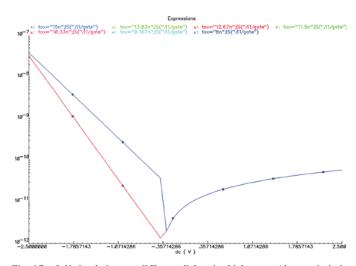

The test structures for electrical measurements are MIS capacitors with a back side electrode of  $\sim 300$  nm evaporated Al. The capacitors are electrically characterized by means of C-V (Fig. 1) and I-V (Fig. 2) curves. The effective dielectric constant  $\varepsilon_{\rm eff}$  of the films is determined from the capacitance  $C_0$  at an accumulation using ellipsometrically measured values of d. The oxide charge  $Q_f$  is evaluated from the C-V curves. The I-V curves are recorded at both polarities with a voltage ramp rate of 0.1 V/s, using Keithley 236 source measurement unit. Temperature dependent  $(20-100\,^{\circ}\text{C})\ I-V$  measurements are performed in order to obtain a deeper insight into the conduction mechanisms governing the current through the structures as well as the energy location of traps participating in these processes. All measurements are carried out in a dark chamber [10].

The C-V measurements are given in Fig. 1. Frequency range of 50 kHz  $\div$  100 kHz is selected in order to minimize the effects of the equivalent series-parallel circuit – at lower frequencies the role of the parallel shunting resistance is increasing while at higher frequencies the series substrate resistance is becoming an important factor [11].

Fig. 1. C-V characteristics measured at 50 kHz, 100 kHz, and 1 MHz.

Fig. 2. I-V characteristics measured with Keithley 236 across 10 nm and 15 nm  $HfO_2$ - $Ta_2O_5$  capacitor stacks.

### III. MODEL FORMULATION AND PARAMETER EXTRACTION

## A. Modeling C-V Characteristics

To adjust the model all parameters they need to be properly extracted from measurement data. The designed model has the typical capacitor input parameters – gate area, dielectric thickness, and substrate type of conductivity (p- or n-doped) which are further customized in the schematics. Other important parameters for the component performance are permittivity, substrate doping concentration, and flat band voltage. The effective permittivity is analyzed in [10] where it is extracted  $\varepsilon_{\rm eff} \approx 9$  from the 100 kHz C–V curve. The methodology, described in [12], provides an easy way for calculation of the doping concentration and the flat band voltage.

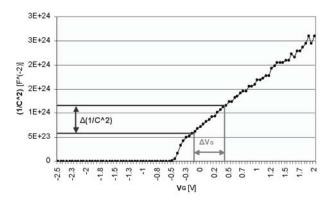

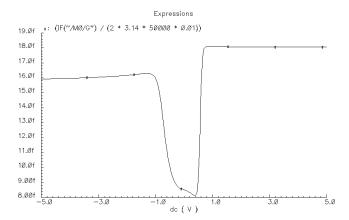

The substrate doping concentration ( $N_{SUB}$ ) is related to the slope of the  $1/C^2$  curve versus the  $V_G$  bias voltage [12] which is shown on Fig. 3.

Therefore it can be directly extracted and calculated as follows [12]:

$$N_{SUB} = \frac{2}{q \varepsilon_{Si} A^2} \left[ \frac{\Delta \left( \frac{1}{C^2} \right)}{\Delta V_G} \right] \tag{1}$$

where q – electron charge (1.60219×10<sup>-19</sup> C), A – gate area (in cm<sup>2</sup>),  $\varepsilon_{\text{Si}}$  – substrate permittivity (1.305×10<sup>-12</sup> F/cm for Si).

Fig. 3 shows the extraction of slope after the onset of depletion based on which the substrate doping concentration was calculated on  $N_{SUB} = 1.25 \times 10^{15} \text{ cm}^{-3}$ .

# 1/C^2 vs gate voltage bias at 50kHz for 10nm HfO2-Ta2O5

Fig. 3. Curve of  $1/C^2$  vs.  $V_G$  at frequency of 50 kHz. The typical increasing slope after the onset of depletion is observed.

The flat band voltage and the doping concentration profile were not directly extracted from measurements due to the low accuracy of the method for bigger values of the interface trap density  $(0.5 \div 1 \times 10^{12} \ cm^{-2} eV^{-1}$  according to [10]). These parameters were fitted in the model according to the measurements.

# B. Model Equations

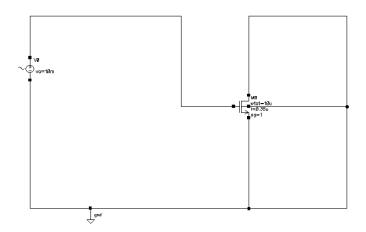

The modeled high-*k* dielectric structure might be considered as an upgrade to the state-of-the-art CMOS technology for which the BSIM3v3 model provides one of the most advanced approximations to device physics. Therefore the equations for simulating the *C–V* characteristics are based on BSIM3v3 equations which allow relatively easy applicability across different technologies. The existing standard BSIM3v3 MOSFET in the design kit can be simulated as MOS capacitor if the source, bulk, and drain are connected as shown on the schematics of Fig. 4.

Fig. 4. Bench circuit for simulation of C-V characteristics of capacitor-connected MOSFET.

In Fig. 4 the MOS transistor is n-channel with default parameters for the S35D3 technology of the 0.35- $\mu$ m CMOS design kit of AMS.  $V_0$  is a sinusoidal voltage source with fixed amplitude of 10 mV and DC voltage sweep between -5 V  $\div$  +5 V. The C-V characteristics are simulated in AC mode by plotting the capacitance as a calculation based on the amplitude of the current through the gate node for a frequency of 50 kHz. The simulation of the C-V characteristics is shown on Fig. 5:

Fig. 5. *C-V* characteristics simulated by the capacitor-connected MOSFET model. The onset of strong inversion is observed after threshold voltage.

That graph shows onset of strong inversion after the threshold voltage because of the dominant impact of the doped source and drain regions. This is not the case with the analyzed  $HfO_2$ - $Ta_2O_5$  capacitor stacks because it has no drain and source. Therefore a modification of the BSIM3v3 equations is required. The portion of the Verilog-A code, which describes the intrinsic capacitance, was extracted, simplified, and embedded in a two-node component operating as capacitor in the C-V simulation circuit.

The intrinsic capacitance equation is a sum of three charge types – the channel majority accumulation charge  $(Q_{ac0})$ , the channel minority inversion charge  $(Q_{inv})$ , and the substrate fixed charge  $(Q_{sub0})$ :

$$Q_{gate} = Q_{inv} + Q_{ac0} + Q_{sub0} \tag{2}$$

The charge  $Q_{inv}$  can be omitted because it has dominant contribution after onset of inversion [13]. It describes the rapid exponential increase of minority carriers density which is dominating the slower increase of the depletion layer charge; this results in capacitance jump-up after the threshold voltage. The measurements show that the C-V slope is almost flat in strong inversion (Fig. 1) because the minority carriers contribute no capacitance and they screen further increase of the depletion width [12], [14].

The channel majority accumulation charge  $(Q_{ac0})$  has dominant influence on the accumulation and depletion regions while in inversion the substrate fixed charge  $(Q_{sub0})$  is with bigger impact. Therefore the model for the C-V curve can be split in two parts – description of accumulation and depletion regions by the parameter  $Q_{ac0}$  and description of inversion region by the parameter  $Q_{sub0}$ .

The charge  $Q_{ac0}$  is given in [12] by the following equations:

$$Q_{ac0} = WLC_{ox}^{eff} \left( V_{FB}^{eff} - V_{FB} \right) \tag{3}$$

where  $V_{FB}^{eff}$  is the effective flat-band voltage which smoothens the transition between accumulation and depletion [13]. It is calculated by:

$$V_{FB}^{eff} = \begin{cases} V_{FB} - 0.5 \left( V_3 + \sqrt{V_3^2 + 4\delta_{3,1}V_{FB}} \right) & \text{if } V_{FB} \ge 0 \\ V_{FB} - 0.5 \left( V_3 + \sqrt{V_3^2 - 4\delta_{3,1}V_{FB}} \right) & \text{if } V_{FB} < 0 \end{cases}$$

(4)

$$V_3 = V_{FB} - V_{GS} - \delta_{3.2} \tag{5}$$

$V_{GS}$  – bias voltage across the capacitor stack between gate and substrate electrodes,  $\delta_{3,1}$  and  $\delta_{3,2}$  – constants with default value  $\delta_{3,1} = \delta_{3,2} = 0.02$  V (these constants were split in order to separately study their influence),  $C_{ox}^{eff}$  – total capacitance per unit area [14] expressed as the series combination of the silicon capacitance per unit area  $C_{cen} = \varepsilon_{Si}/T_{cen}$

The oxide capacitance per unit area  $C_{ox} = \varepsilon_{ox}/t_{ox}$  is:

$$C_{ox}^{eff} = \frac{C_{ox}C_{cen}}{C_{ox} + C_{cen}} \tag{6}$$

$\varepsilon_{Si}$  and  $\varepsilon_{ox}$  – dielectric constants of the silicon and the dielectric layer,  $t_{ox}$  is the thickness of the dielectric layer.  $T_{cen}$  is calculated following the equations given in [15]. In  $T_{cen}$  expressions the parameter  $A_{CDE,Nch}$  is an exponential coefficient characterizing the charge width in accumulation and depletion [13]. It also depends on  $N_{ch}$  which is the doping concentration in the inversion channel for MOSFET (directly under the surface of the dielectric layer):

$$A_{CDE,Nch} = A_{CDE} \times \left(\frac{N_{ch}}{2 \cdot 10^{16}}\right)^{-0.25} \tag{7}$$

In BSIM3v3 the default of  $A_{CDE}$  is 1.

The substrate fixed charge ( $Q_{sub0}$ ) is given in [15] by:

$$Q_{sub0} = \begin{cases} WLC_{ox}^{eff} \gamma_2 \left( \sqrt{\frac{K_1^2}{4} + Tmp} - \frac{K_1}{2} \right) & \text{if } Tmp \ge 0 \\ WLC_{ox}^{eff} \gamma_2 \times Tmp & \text{if } Tmp < 0 \end{cases}$$

(8)

where

$$Tmp = V_{GS} - V_{FB}^{eff} - V_{gst}^{effCV}$$

(9)

$V_{gst}^{effCV}$  – effective voltage ( $V_{GS} = V_{th}$ ) function introduced to describe the channel charge characteristics from sub-threshold to strong inversion [13] where the capacitance is increasing rapidly. That function can be omitted because the capacitance remains almost flat in strong inversion as observed from the C-V measurements  $\gamma_2$  – body-effect in the bulk [15].

The initial model should be fitted in order to minimize the error with respect to the measurements. An accurate assessment of the fitting is given by calculating the integral error which is calculated as an average of the errors inside each interval.

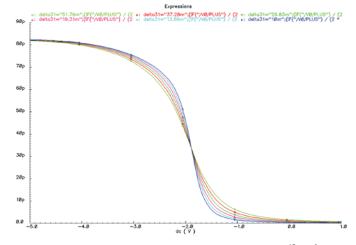

- $--A_{\it CDE}$  has an impact both in the accumulation and depletion regions.

- $--N_{ch}$  has an impact both in the accumulation and depletion regions.

- --  $\delta_{3,1}$  has a significant impact in the depletion region by changing the slope of the curve which is visible for  $N_{ch} > 10^{16} \, \text{cm}^{-3}$ .

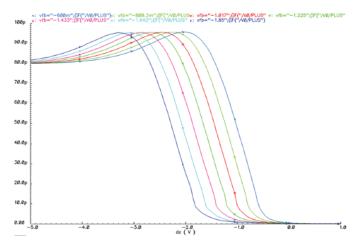

- --  $V_{FB}$  and  $\delta_{3,2}$  these two parameters move equidistantly the curve across the *x*-axis (the applied bias voltage), therefore with biggest impact on the depletion region has a significant impact in the depletion region by changing the slope of the curve which is visible for  $N_{ch} > 10^{16} \, {\rm cm}^{-3}$ .

The complexity of the equations and the shape of the C-V curve does not allow direct fitting of these parameters for the whole bias range. More flexible approach is to define values of the empirical coefficients ( $\delta_{3,1}$  and  $\delta_{3,2}$ ) for different bias voltage ranges.

#### Measured CV characteristics for 10nm HfO2-Ta2O5

Fig. 6. *C–V* characteristics split into regions for fitting. In each region the corresponding parameters for fitting are shown.

The fitting started with finding the optimal value of the flatband voltage which moved the C-V curve in the desired bias range. Then the surface doping concentration ( $N_{ch}$ ) was fitted in accumulation in combination with the coefficient  $A_{CDE}$ . This allowed further fine fitting of the slope in depletion by changing only  $\delta_{3,1}$  and  $\delta_{3,2}$ . The parameters for fitting in the corresponding regions of the C-V curve are illustrated on Fig. 6.

The product from the first fitting iterations is the optimized values given in Table I.

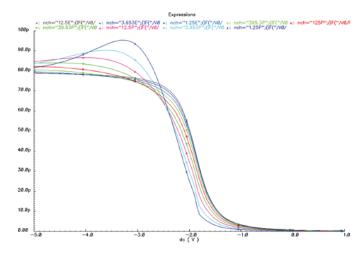

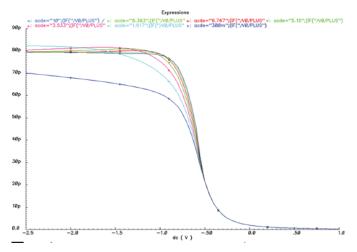

In the figures below we present results from the analysis of the impact of the fitting parameters to the C-V characteristics. The influence of  $A_{CDE}$  and  $N_{ch}$  parameters on the C-V characteristics is given on Fig. 7–9. The impact of  $\delta_{3,1}$ ,  $\delta_{3,2}$  and  $V_{FB}$  parameters is given in Fig. 10–13.

As it can be observed the C-V measurements fit very well with the simulation results of  $Q_{sub0}$  for bias voltage greater than -0.4 V. Therefore the expressions of the charge  $Q_{ac0}$  can be replaced with the expressions of  $Q_{sub0}$  for  $V_{GS} \ge V_{FB} + 0.15$ .

${\bf TABLE~I}$  FITTED PARAMETER VALUES DESCRIBING THE  $\it C-V$  CHARACTERISTICS

| Parameter                                           | Value                                  | Bias voltage range [V] <sup>a</sup> |

|-----------------------------------------------------|----------------------------------------|-------------------------------------|

| Flat-band voltage, $V_{FB}$ a                       | – 0.55 V                               | $(-\infty, +\infty)$                |

| Surface doping concentration, $N_{ch}$ <sup>a</sup> | $1.25 \times 10^{18} \text{ cm}^{-3}$  | $(-\infty, +\infty)$                |

| $\delta_{3,1}$                                      | 0.02 V                                 | $<(V_{FB}-1.2)$                     |

| $\delta_{3,1}$                                      | $0.028 \text{ V} \div 0.048 \text{ V}$ | $(V_{FB}-1.2) \div (V_{FB}-0.05)$   |

| $\delta_{3,1}$                                      | $0.038 \text{ V} \div 0.016 \text{ V}$ | $(V_{FB}-0.05) \div (V_{FB}-0.11)$  |

| $\delta_{3,1}$                                      | 0.01 V                                 | $> (V_{FB} - 0.11)$                 |

| $\delta_{3,2}$                                      | 0.02 V                                 | $<(V_{FB}-1.45)$                    |

| $\delta_{3,2}$                                      | 0.24 V                                 | $> (V_{FB} - 1.45)$                 |

$<sup>^{\</sup>rm a}$  So defined  $V_{FB}$  and  $N_{ch}$  are technology constants related to flat-band voltage and surface doping concentration.

Fig. 9. C-V characteristics at different  $N_{ch}$ .

Fig. 7. C-V characteristics at different  $A_{CDE}$  and  $N_{ch} = 1.25 \times 10^{17}$  cm<sup>-3</sup>.

Fig. 10. C-V characteristics at different  $\delta_{3,1}$  and  $N_{ch} = 1.25 \times 10^{16}$  cm<sup>-3</sup>.

Fig. 8. C-V characteristics at different  $A_{CDE}$  and  $N_{ch} = 1.25 \times 10^{18}$  cm<sup>-3</sup>.

Fig. 11. C-V characteristics at different  $\delta_{3,1}$  and  $N_{ch} = 1.25 \times 10^{17}$  cm<sup>-3</sup>.

Fig. 12. C-V characteristics at different  $V_{FB}$ .

Fig. 13. C-V characteristics at different  $\delta_{3,2}$ .

Fig. 14–15 show the results from parametric analysis with the geometry parameters which validates the model flexibility.

Fig. 14. *C–V* characteristics at different gate lengths *l*.

Fig. 15. C-V characteristics at different oxide thicknesses  $t_{ox}$ .

The integral error of the mismatch between the simulations and measurements curves was calculated to be  $err_{avg} = 3.35 \%$ .

## C. Modeling I-V Characteristics

The I–V characteristics can be also split into two regions described with separate equations for the current density J:

-- Accumulation and depletion region for  $V_{GS} \leq V_{FB} + 0.25$  where the current density follows exponential dependence on the applied bias voltage:

$$J(V_{GS}) = a_1 e^{-b_1 V_{GS}} (10)$$

-- Inversion region for  $V_{GS} > V_{FB} + 0.15$  where the current density follows linear dependence on the bias voltage:

$$J(V_{GS}) = a_2 + b_2 V_{GS} (11)$$

The fitting was based on the measurement results from both the 10 nm and 15 nm capacitor stacks (Fig. 2). Lower currents are observed with thicker dielectric layers in accumulation and depletion regions. Hence, different values for  $a_1$  and  $b_1$  are needed. At the same time no significant thickness dependence exists in the inversion region where the current seems to be more fluctuating due to the unstable conditions for forming the inversion layer. Therefore the characteristics can be approximated with same linear equation. On Fig. 16 the approximations for the capacitor stacks with both thicknesses are displayed.

TABLE II COEFFICIENTS FOR I-V APPROXIMATION

| Coefficient | 10 nm thickness       | 15 nm thickness       |

|-------------|-----------------------|-----------------------|

| $a_1$       | 1.0×10 <sup>-11</sup> | $2.0 \times 10^{-13}$ |

| $b_1$       | 3.3                   | 4.8                   |

| $a_2$       | $8.0 \times 10^{-12}$ |                       |

| $b_2$       | $2.0 \times 10^{-11}$ |                       |

Fig. 16. *I–V* measurements vs. the proposed approximations for 10 nm and 15 nm capacitor stacks from HfO<sub>2</sub>-Ta<sub>2</sub>O<sub>5</sub> (*y*-axis is in logarithmic scale).

The thickness dependence will be modeled even more accurately after gathering more characterization data. The current model was created to generate only two *I–V* curves:

- -- For thickness less than 12.5 nm using the values from the second column of Table II.

- -- For thicknesses greater than 12.5 nm using the values from the third column of Table II.

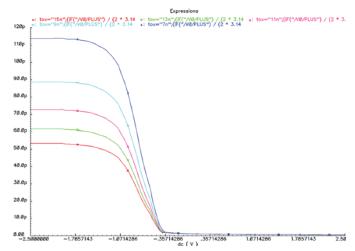

The leakage current model was simulated using similar test bench like for the C-V simulation (Fig. 4). The corresponding voltage source, type of analysis and current selected for plotting were replaced from AC to DC. Afterwards the I-V model was validated by parametric analysis versus thickness (Fig. 17). The average integral error of the mismatch between the simulations and measurements is  $err_{avg} = 8.83 \%$ .

Fig. 17. I–V simulation vs. different dielectric thicknesses (the y-axis is in logarithmic scale). The curve complies with the characterization results.

#### IV. VERILOG-A SIMULATION

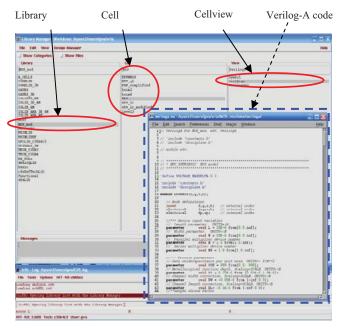

The simulated model was coded in Verilog-A and implemented in Cadence Spectre circuit simulator as external model as standard cell in design kit's library (Fig. 18).

Fig. 18. Workflow of circuit simulation in Cadence Design Framework II and implementation of Verilog-A code as library cell.

Below we provide a briefed listing of the full Verilog-A code of the model.

```

// Device Parameters //

parameter real L

= 100.0e-6;

parameter real W

= 100.0e-6;

parameter real TYPE

= 1.0;

parameter real TOX

= 100.0e-10;

real

acde, tox, cox, nch, tnom, vgs, Vgs;

1, w, delta_3_1, delta_3_2;

real

real

Vtm0, T0, T1, T2, T3, tmp;

real

nsub, gamma2, k1, vfb, ldeb;

// Charge model related variables

real

qgate, Qgate, Qsub0;

real

cqgate;

Vfb, CoxWL, Qac0, Vfbeff;

real

real

Cox, V3, Tox, Coxeff, CoxWLcen, Tcen,

Ccen, LINK, V4;

// Leakage model related variables

real

igate, a1, b1;

// Calculation of the charge in accumulation //

Tox = 1.0e8 * tox;

= (Vgs - vfb) / Tox;

= T0 * acde;

Tcen = ldeb * exp(tmp);

LINK = 1.0e-3*tox;

= ldeb - Tcen - LINK;

= \exp(0.5*\ln(V3*V3 + 4.0 * LINK * ldeb));

V/4

Tcen = 1deb - 0.5 * (V3 + V4);

Ccen = `EpsSi / Tcen;

= Cox / (Cox + Ccen);

= T2 * Ccen;

Coxeff

CoxWLcen = CoxWL * Coxeff / Cox;

Qac0 = CoxWLcen * (Vfbeff - vfb);

// Calculation of the charge in depletion //

T0 = 0.5 * k1;//ok119

T3 = Vgs - Vfbeff;

```

```

if (T3 < 0.0)

begin

T1 = T0 + T3 / k1;

end

else

begin

T1 = \exp(0.5*\ln(T0 * T0 + T3));

end

Qsub0 = CoxWLcen * k1 * (T1 - T0);

// The following statements replace Qac0 with

Qsub0 for the depletion region //

if((vfb-vgs) \leq -0.15)

qgate = Qsub0;

else

qgate=Qac0;

// Expressing the current as first

derivative of the charge //

Qgate = qgate;

cqgate = TYPE * ddt(Qgate);

I(gate, bulk) <+ cqgate;</pre>

// IV model //

if (tox < 12.5e-9)

begin

a1 = `A1;

b1 = `B1;

end

else

begin

a1 = `A2;

b1 = `B2;

end

if((vfb-Vgs) >= -0.25)

igate = a1*exp(-b1*Vgs)*w*1/(100e-6*100e-6);

if ((vfb-Vgs) < -0.25)

igate = (a2 + b2*Vgs)*w*1/(100e-6*100e-6);

I(gate, bulk) <+ igate;

```

## V. CONCLUSION

A Verilog-A formulation of circuit simulation model for a MOS capacitor using high-k HfO<sub>2</sub>–Ta<sub>2</sub>O<sub>5</sub> mixed layer structure was developed. The model proceeds from BSIM3v3 model equation core to simulate C-V and I-V characteristics of the modeled structure. The simulation results were validated against the measurements of an experiment.

The simulations were performed in Spectre circuit simulator within Cadence CAD environment. They demonstrated very good agreement to the measurements -3.35% accuracy for C-V measurements and 8.83% for I-V measurements.

On the other hand, the model realization represents a straightforward example of an all-purpose methodology for coding compact model equations in a portable, open-source environment applicable to various simulation platforms.

The developed model allows for further fine-tuning in order to obtain better accuracy. Subject to additional study are the dependence of the capacitance from the frequency of gate-to-bulk voltage, the dependence of the capacitance and the leakage current from the dielectric thickness, and the real surface impurity concentration under the dielectric film.

#### REFERENCES

- [1] G. Angelov, T. Takov, and St. Ristiç "MOSFET Models at the Edge of 100-nm Sizes", in *Proc. 24th Intl. Conf. on Microelectronics (MIEL* 2004), Niš, Serbia and Montenegro, 2004, vol. 1, pp. 295-298.

- [2] S. Deleonibus, Electronic Device Architectures for the Nano-CMOS Era. From Ultimate CMOS Scaling to Beyond CMOS Devices, Pan Stanford Publishing Pte., Singapore, 2009.

- [3] K. J. Kuhn, "CMOS scaling beyond 32nm: Challenges and opportunities", in *Proc. 46th ACM/IEEE Design Automation Conf.* (DAC 2009), San Francisco, CA, 2009, pp. 310–313.

- [4] The International Technology Roadmap for Semiconductors 2009 Edition [Online]. Available: http://www.itrs.net/Links/2009ITRS/Home2009.htm

- [5] R. Chau et. al. "Application of High-k Dielectrics and Metal Gate Electrodes to Enable Silicon and Non-Silicon Logic Nanotechnology", *Microelectronic Engineering*, 2005, vol.80, pp. 1-6.

- [6] G. D.Wilk, R. M.Wallace, and J. M. Anthony, "High-k Gate Dielectrics: Current Status and Materials Properties Considerations," *J. Appl. Phys.*, 2001, vol. 89, pp. 5243–5275.

- [7] M. Houssa, ed., "High-k Gate Dielectrics", *Institute of Physics Publishing, Bristol and Philadelphia*, 2004. ISBN 0-7503-0906-7.

- [8] E. Atanassova and A. Paskaleva, "Challenges of Ta<sub>2</sub>O<sub>5</sub> as high-k dielectric for nanoscale DRAMs", *Microelectronics Reliability* 47(6), 2007, pp. 913-923.

- [9] M. Mierzwinski, P. O'Halloran, B. Troyanovsky, R. Dutton, "Changing the paradigm for compact model integration in circuit simulators using Verilog-A", *Technical Proc. 2003 Nanotechnology Conf. and Trade Show (Nanotech 2003)*, February 2003, vol. 2, pp. 376–379.

- [10] E. Atanassova, M. Georgieva, D. Spassov, and A. Paskaleva, "High-k HfO<sub>2</sub>-Ta<sub>2</sub>O<sub>5</sub> mixed layers: Electrical characteristics and mechanisms of conductivity", *Microel. Engin.* 87, 2010, pp. 668-676.

- [11] K. J. Yang, C. Hu, "MOS Capacitance Measurements for High-Leakage Thin Dielectrics", *IEEE Transactions on Electron Devices*, Vol. 46, No. 7, July 1999.

- [12] C-V Characterization of MOS Capacitors Using the Model 4200-SCS Semiconductor Characterization System, KEITHLEY Application Note Series, No. 2896.

- [13] Y. Cheng, et. al. "BSIM3v3.1 User's Manual", Memorandum No. UCB/ERL M97/2, 1997.

- [14] E. H. Nicollian and J. R. Brews, "MOS (Metal Oxide Semiconductor) Physics and Technology", Wiley-Interscience, New York, 1982.

- [15] Cadence Design Systems, Inc., Staff, "Cadence Circuit Components and Device Models Manual", Product Version 6.0 Spectre, Cadence Design Systems, Inc. 11/2005.

**George V. Angelov** (M'2004) is born on 19.02.1976 in Sofia, Bulgaria. He obtained a Master of Physics degree from Sofia University "St. Kliment Ohridski", Sofia, Bulgaria in 1999 and defended his PhD thesis at the Technical University of Sofia, Bulgaria in 2008.

He worked for the Technology Centre–Institute of Microelectronics between 1998-2001 as modeling researcher, and for Hybrid Integrated Circuits Ltd. between 2001-2003 as process engineer and quality manager.

Since 2007 G. V. Angelov is assistant professor at the Technical University of Sofia, Dept. of Microelectronics, ECAD Laboratory.