#### Invited paper

# **Rare Earth Silicate Formation:** A Route Towards High-k for the 22 nm Node and Beyond

Ivona Z. Mitrovic and Stephen Hall

Abstract- Over the last decade there has been a significant amount of research dedicated to finding a suitable high-k/metal gate stack to replace conventional SiON/poly-Si electrodes. Materials innovations and dedicated engineering work has enabled the transition from research lab to 300 mm production a reality, thereby making high-k/metal gate technology a pathway for continued transistor scaling. In this paper, we will present current status and trends in rare earthbased materials innovations; in particular Gd-based, for the high-k/metal gate technology in the 22 nm node. Key issues and challenges for the 22 nm node and beyond are also highlighted.

Keywords— gadolinium silicate, interfacial layer, lanthanides, rare earth oxides.

## 1. Introduction

A 32 nm process technology, including a high-k dielectric and metal-gate has been announced [1]-[5]. The equivalent oxide thickness (EOT) of the high-k dielectric has been reduced from 1.0 nm on 45 nm node to 0.9 nm [1] on the 32 nm process, while gate length has been reduced to 30 nm. Transistor gate pitch continues to scale  $0.7 \times \text{ev}$ ery two years - with 32 nm providing the tightest gate pitch in the industry. The key industrial players are Intel Corporation, IBM alliance (with AMD, Chartered, Freescale, Infineon, Samsung, ST and Toshiba), TSMC, NEC, Panasonic in collaboration with Renesas. Different integration strategies have been employed by various parties involved, namely a replacement gate [6], [7] or a conventional gatefirst approach [8], [9]. In the latter, the gate stack is formed before the source and drain, as in a conventional complementary metal oxide semiconductor (CMOS) process, while the former is a gate-last approach. Moving beyond the planar transistor, IBM, AMD, Freescale and Toshiba have recently presented a fin field effect transistor (Fin-FET) with high-k and metal gates for the 32 nm node and beyond [3].

A static random access memory (SRAM) cell was devised at areas down to 0.128  $\mu$ m<sup>2</sup>. Using 22 nm design rules, the cell was fabricated using a CMOS process flow and e-beam lithography. In the cell, fin pitch was 80 nm, gate pitch 110 nm and physical gate length 30 nm. To enable high-k and metal gates, chemical vapour deposition (CVD)based HfO<sub>2</sub>, physical vapour deposition (PVD) TiN and polysilicon were deposited on the fin portion of the device.

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

4/2009

TSMC has also announced a 32 nm process [4], which includes a high-k/metal-gate scheme based on a gate-first technology. A 0.15  $\mu$ m<sup>2</sup> SRAM cell was developed by using a Hf-based material and 193 nm immersion lithography with a numerical aperture of 1.35. The high-k material has been scaled to 1 nm, at 30 nm physical gate length and 130 nm gate pitch. The team of NEC and Toshiba Corporation has developed a 32 nm process, with a single-exposure lithography technology and a gate-first high-k/metal-gate process [5]. They demonstrated a SRAM cell of  $0.124 \,\mu m^2$ and a gate density of 3650 KGate/mm<sup>2</sup>. From the relevant publications and press releases, it is evident that Hf-based dielectrics are retained for the 32 nm node leaving other dielectrics for consideration at further technology nodes. Physical gate length scaling, from 35 nm, in the 45 nm generation, to 30 nm in the 32 nm generation, is enabled by high-k dielectric scaling and shallow junction engineering [10].

Low standby power (LSTP) technology requirements in the near term years according to the International Technology Roadmap for Semiconductors (ITRS) [11] are listed in Table 1. As can be seen, more aggressively scaled EOT is required in order to reach the specification for the 22 nm node. This leads to stringent control of interfacial oxide layer, either by reducing its thickness or by increasing its k-value. A good interface requires either that the oxide is amorphous, or that it is epitaxial and lattice-matched to the underlying silicon [12]. Amorphous oxides represent a low-cost solution; nonetheless, the challenge is to keep these materials amorphous even after post-deposition high temperature processing in order to avoid increased surface roughness and additional leakage due to the formation of grain boundaries, as shown in many investigations [13]–[16]. Another approach is based on the development of epitaxial metal oxides grown directly on silicon surfaces [12]. It is known that for given values of MOS leakage current and insulator thickness, the dielectric constant, k, and the offset value between oxide and silicon energy bands,  $\Delta E$ , are bound roughly by a hyperbolic relation  $k \cdot \Delta E = C_E$ , where  $C_E$  is a constant. Engstrom *et al.* [17] have suggested that a value of  $C_E \approx 70$  eV is necessary for the 22 nm bulk LSTP node, while the corresponding figure for silicon-on-insulator (SOI) technology is in the range of 30-40 eV. Rare earth (RE) oxides offer interesting properties to fulfil such requirements: a high dielectric constant [17], a high band gap and suitable band offsets with respect to Si [18], sufficiently high breakdown strength,

| Year in production                                                                                                        | 2008 | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 |  |

|---------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|--|

| MPU/ASIC metal $1\frac{1}{2}$ pitch [nm] (contacted)                                                                      | 59   | 52   | 45   | 40   | 36   | 32   | 28   | 25   |  |

| Physical length gate for high performance logic [nm]                                                                      | 29   | 27   | 24   | 22   | 20   | 18   | 17   | 15   |  |

| Physical gate length for LSTP (Lg)                                                                                        |      |      |      |      |      |      |      |      |  |

| Extended planar bulk and DG [nm]                                                                                          | 38   | 32   | 29   | 27   | 22   | 18   | 17   | 15   |  |

| UTB FD [nm]                                                                                                               | *    | *    | *    | *    | *    | 20   | 18   | 17   |  |

| EOT                                                                                                                       |      | •    | •    | •    |      | •    | •    |      |  |

| Extended planar bulk [nm]                                                                                                 | 1.6  | 1.5  | 1.4  | 1.3  | 1.2  | 1.1  | *    | *    |  |

| UTB FD [nm]                                                                                                               | *    | *    | *    | *    | *    | 1.2  | 1.1  | 1.0  |  |

| DG [nm]                                                                                                                   | *    | *    | *    | *    | *    | *    | *    | 1.1  |  |

| Maximum gate leakage current density $(J_{g,limit})$                                                                      |      |      |      |      |      |      |      |      |  |

| Extended planar bulk [mA/cm <sup>2</sup> ]                                                                                | 81   | 94   | 110  | 120  | 140  | 150  | *    | *    |  |

| UTB FD [A/cm <sup>2</sup> ]                                                                                               | *    | *    | *    | *    | *    | 150  | 170  | 180  |  |

| DG [A/cm <sup>2</sup> ]                                                                                                   | *    | *    | *    | *    | *    | *    | *    | 190  |  |

| * delineate one of two time periods: either before initial production ramp has started for ultra-thin body fully depleted |      |      |      |      |      |      |      |      |  |

| (UTB FD) SOI or double-gate (DG) MOSFETs, or beyond when planar bulk or UTB FD MOSFETs have reached                       |      |      |      |      |      |      |      |      |  |

| the limits of practical scaling.                                                                                          |      |      |      |      |      |      |      |      |  |

Table 1

Low standby power technology requirements – near term years [11]

extremely low leakage current, and well-behaved interface properties. Their key advantages for advanced CMOS are:

- thermal stability;

- a feature to shift the work function of a metal gate towards n-type and thus engineer a transistor threshold voltage [19], [20];

- a reduction of the low-*k* interfacial layer (IL) thickness.

An important consideration in choosing an alternative high-k dielectric is its compatibility with Si, and metal silicates have attracted much recent attention [21]-[23]. The presence of silicon leads to improved metal oxide/silicon interface stability and reduced leakage currents. This in turn has generated interest in the deposition of lanthanide silicates, such as Gd-silicate [24], La-silicate [25], Prsilicate [26], [27]. A silicate formation is known to occur when a rare earth oxide is in contact with a Si-containing dielectric or a silicon substrate in the presence of oxygen [23]. As such, it can be used to consume the typical SiO<sub>2</sub>-like interfacial layer between high-k and silicon substrate or to enhance its k-value. In this paper, we will show that RE silicate formation is one of the possible pathways towards scaling beyond the 22 nm node. In particular, our recent work on optimization of GdSiO-based gate stack is reviewed and results presented on thermal stability and mechanisms of silicate formation.

# 2. Rare Earth Oxides and Silicates

Rare earth oxides are attractive materials for gate dielectric application, and in particular the lanthanide oxides group (LnO's). Lanthanides refer to a series of 15 elements from La to Lu in the periodic table, which have similar but gradually changing characteristics [28]. The LnO's can have different stoichiometries due to the multiple oxidation states (+2, +3, and +4) of the metals. This leads to oxides with different structural phases including two cubic phases, namely, the calcium fluoride structure for the Ln(IV) only, and the bixbyite structure for Ln(III) [29]. Lanthanide oxides with more than one valence state are not the best choice for CMOS processing because of the coexistence of phases with different oxygen contents and possible transformations between them, or even the occurrence of mixed valence-state structures [30], [31]. A summary of the key properties of RE LnO's is given in Table 2 ([17], [29] and references therein). Those deemed suitable for application are now described.

The RE oxides, such as La<sub>2</sub>O<sub>3</sub> [32], [33], Pr<sub>2</sub>O<sub>3</sub> [34]–[37], Gd<sub>2</sub>O<sub>3</sub> [38], and Nd<sub>2</sub>O<sub>3</sub> [39], [40] have been investigated. They are good insulators due to their large band gaps, high dielectric constants (13–16 for Gd<sub>2</sub>O<sub>3</sub>, 25–30 for La<sub>2</sub>O<sub>3</sub> [17], 15–25 for Pr<sub>2</sub>O<sub>3</sub> [41]) and good thermodynamic stability on silicon even at high temperatures, i.e., when heated in contact with silicon will not directly react to form silicide, metal, or silicon oxide [42]. Another attractive feature of Pr<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub>, and Nd<sub>2</sub>O<sub>3</sub> is their relatively close lattice match to silicon (2a<sub>Si</sub> = 1.090 nm), which offers the possibility of epitaxial growth, eliminating problems related to grain boundaries in polycrystalline films.

Silicate formation of binary lanthanide oxides in contact with SiO<sub>2</sub> has been the subject of many studies [24], [40], [43]–[46] whereby the SiO<sub>2</sub> IL is consumed during a high temperature step. The process has been demonstrated for La<sub>2</sub>O<sub>3</sub> [47], [48] or Gd<sub>2</sub>O<sub>3</sub> [49], [50] deposited on SiO<sub>2</sub>.

| Compound                                        | Structure | a[Å]   | c[Å]  | Band gap [eV] | Dielectric constant |

|-------------------------------------------------|-----------|--------|-------|---------------|---------------------|

| Er <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 10.548 |       | 5.3, 5        | 13                  |

| La <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 11.327 |       | 5.5, 6        | 25, 27–30           |

| La <sub>2</sub> O <sub>3</sub> A type polymorph | Hexagonal | 3.937  | 6.129 | 5.5           | 25                  |

| Nd <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 11.08  |       | 4.4           | 16                  |

| Nd <sub>2</sub> O <sub>3</sub> A type polymorph | Hexagonal | 3.829  | 5.997 | 4.4           | 16                  |

| Sm <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 10.92  |       | 5             | 13, 11.4–15         |

| Ho <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 10.606 |       | 5, 5.2        | 13.1                |

| Gd <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 10.813 |       | 5.3, 6.4      | 13.7, 13.6          |

| Dy <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 10.665 |       | 4.9           | 13.1                |

| Lu <sub>2</sub> O <sub>3</sub>                  | Bixbyite  | 10.391 |       | 5.4, 6        | 12.5                |

| Pr <sub>2</sub> O <sub>3</sub>                  | Hexagonal | 3.857  | 6.916 | 4.6           | 14.9, 25.4 [41]     |

Table 2Properties of RE Ln2O3 oxides [17], [29]

The extent of silicate formation depends on temperature, time (spike anneal) and the ion radius of the RE element [31], [51], [52]. A unique property of RE elements is "lanthanide contraction", a term which refers to the observation that the ion radii of rare earth elements decrease gradually as the atomic number increases. The quantity of Si-O-Ln bonds increases as the post-annealing temperature rises, and this increase depends strongly on the ion radii of the RE elements. As a result, metal-oxides with larger ion radii easily form LnSiO (silicate) layers. An alternate explanation can be deduced from thermodynamic arguments [52]. Furthermore, the quantity of Si-O-Si bonds increases after annealing independent of the element.

Rare earth oxide and silicate films have been deposited by various methods including atomic and electron beam evaporation [24], [38], [49], [50], [53], molecular beam epitaxy (MBE) [40], metal organic chemical vapour deposition (MOCVD) and atomic layer deposition (ALD) [33], [35], [54], [55]. CVD and ALD techniques allow the controlled growth of highly conformal films on planar and high-aspect ratio substrates. Recent developments in precursors for the MOCVD and ALD of lanthanide oxides  $LnO_x$  and silicates  $LnSi_xO_y$  (Ln = Pr, Gd, La and Nd) have been described in [55], with emphasis on the effect of the precursors molecular structure on process chemistry and layer purity.

# 3. GdSiO: High-*k* Material for the 22 nm Node

#### 3.1. Gd<sub>2</sub>O<sub>3</sub> Studies

The Gd<sub>2</sub>O<sub>3</sub> layers have been studied extensively [38], [52], [56]–[58]. Gd<sub>2</sub>O<sub>3</sub> has been deposited by MOCVD [57], anodic oxidation [59], thermal oxidation [60], [61], MBE [62], [63], e-beam evaporation [49], [50] and ALD [55], [64], [65]. The use of Gd<sub>2</sub>O<sub>3</sub> dielectric layers has been reported for Si [52], [63] and III-V compounds, such as GaN [66], [67] and GaAs [68], [69]. Based on thermody-

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY 4/2009

namic consideration,  $Gd_2O_3$  formed according to equation  $2Gd_2O_3 + 3Si = 4Gd + 3SiO_2$  with  $\Delta G > 100$  kJ, is expected to be stable on Si up to  $1000^{\circ}C$  [42]. Furthermore, Gd is a single valence metal ion (+3); therefore it forms only a single oxide (Gd<sub>2</sub>O<sub>3</sub>) from the reaction with oxygen. This oxide does not exhibit any intermediate metastable states while reacting with oxygen. The effective dielectric constant of the Gd<sub>2</sub>O<sub>3</sub> films is in the range of 7–23 [57]. The reported values for a band gap vary from 5.2 eV [70], [71], 5.3 [29], to 6.4 [17]. The conduction and valence band offsets to Si are larger than 2 eV [62], [71]. The lattice parameter of Gd<sub>2</sub>O<sub>3</sub> in its bixbyite phase is 1.081 nm (Table 2), while Si has a lattice constant  $a_{Si}$  of 0.545 nm, where  $2 \times a_{Si}$  is 0.4% larger than  $a_{Gd_2O_3}$ , which allows for epitaxial growth.

There are reports on electrical properties of epitaxial Gd<sub>2</sub>O<sub>3</sub> thin films grown by MBE [62], [72], with EOT < 1 nm and leakage current density below 1 mA/cm<sup>2</sup>. As can be seen from Table 1, these numbers exceed the requirements for LSTP application predicted for 2012. A careful control of the thermodynamic parameters, such as oxygen chemical potential allows the interface layer change from oxide-like to a silicate-like, and thus leads to larger *k* and lower leakage for the latter one [62]. The impact of rapid thermal anneal (RTA) on structural and electrical properties of crystalline Gd<sub>2</sub>O<sub>3</sub> layers grown on Si has been discussed in [73]. Any degradation of the layers can be significantly reduced by capping with amorphous-Si prior to RTA.

#### 3.2. Academic Cluster Work

The so-called Academic Cluster comprises of four member institutions, namely – Chalmers University of Technology (Sweden), AMO GmbH (Germany), Tyndall National Institute (Ireland) and Liverpool University (UK). We have recently reported an optimized process based on GdSiO for the gate dielectric, consistent with the 22 nm LSTP target [49]. The Gd<sub>2</sub>O<sub>3</sub> layers are deposited by e-beam evaporation [49], [50] and atomic layer deposition [64], [65] on different interfacial silicon dioxide layers (thermal ~1–4 nm, and native ~1 nm). Detailed material properties of the layers are assessed by variable angle (65–75°) spectroscopic ellipsometry (VASE), medium energy ion scattering (MEIS), X-ray diffraction (XRD), high resolution transmission electron microscopy (HRTEM) and X-ray photoelectron spectroscopy (XPS). Electrical characterization including capacitance-voltage and current-voltage techniques is conducted on metal insulator semiconductor (MIS) capacitors with TiN and Au electrodes. The formation of gadolinium silicates has been achieved by RTA annealing of various Gd<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate stacks in the temperature range of 800 to 1050°C and anneal time 1–100 s.

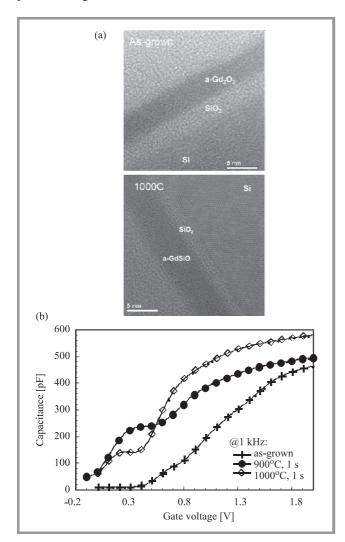

*Fig. 1.* (a) HRTEM images of  $Gd_2O_3/SiO_2$  gate stacks asdeposited by ALD (top) and after RTA at 1000°C for 1 s in N<sub>2</sub> (bottom); (b) *C-V* plots of corresponding MIS devices (Au/*hi*- $k/SiO_2/Si(100)$ ).

The HRTEM images of ALD  $Gd_2O_3/SiO_2$  gate stacks as-deposited and after the RTA @1000°C are shown in Fig. 1(a). The high-*k* dielectric is deposited in amorphous form. Following a 1000°C anneal for 1 s, the intermixing is complete resulting in a 4.6 nm amorphous GdSiO layer. The consumption of interfacial SiO<sub>2</sub> layer is evident after RTA anneal. More importantly, the silicate reaction causes an increase of accumulation capacitance in the associated C - V plots (Fig. 1(b)), and hence the capacitance equivalent thickness (CET) of the gate stack is reduced after RTA. Furthermore, k is ~ 16 and amorphization of the film annealed at 1000°C reduces the leakage current density (9.9 · 10<sup>-7</sup> Acm<sup>-2</sup>) by an order of magnitude compared to the 900°C sample [65].

*Fig.* 2. (a) CET/total deposited thickness versus  $t_{hi-k}/t_{IL}$  ratio and (b) leakage versus CET for various Gd<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate stacks deposited by ALD and e-beam evaporation, on thermal (T) or native oxide (N). I-VI refer to different runs, i.e., various  $t_{hi-k}/t_{IL}$  ratios.

Various ratios of the physical thicknesses of the  $Gd_2O_3/SiO_2(t_{hi-k}/t_{IL})$  gate stack have been explored [64] as shown in Fig. 2. By plotting  $CET/(t_{hi-k} + t_{IL})$  versus  $t_{hi-k}/t_{IL}$  for 1 s anneal time, it can be seen that a value  $t_{hi-k}/t_{IL} \sim 2-2.5$  gives the optimal scaling, that is, the smallest CET of the GdSiO gate dielectric stack. However, this observation needs to be taken equally with the effects of mechanisms involved during RTA anneals on scaling, that is, the way the RTA is performed has shown to be of crucial importance [49]. Specifically, for the same thickness ratios achieved by two deposition processes, e-beam evaporation and ALD, different scaling/CET can be seen after RTA from Fig. 2(b). For ALD processes, RTA was performed in an inert ambient (N<sub>2</sub> or Ar) – RTA1, while

for e-beam evaporation in addition to RTA1, an inert gas is used but with open vacuum valve referred to as RTA2 [49]. GdSiO formation at 900°C by RTA1 results only in slight reduction of CET and this is found to be due to residual oxygen in the process chamber that can diffuse through the films and react at the Si/SiO<sub>2</sub> interface. This is a parasitic effect rather than an intrinsic feature of RTA1; as a result, CET cannot be further reduced as IL re-growth counteracts the consumption due to silicate formation. This explains an increased CET for ALD deposited stacks. The use of RTA2 with open vacuum valve was seen to cause significant reduction of IL re-growth and thus consumption of the IL dominates during silicate formation which further enhances scaling. Using the RTA2 in combination with a preceding post deposition annealing (PDA) treatment enabled to achieve GdSiO gate stack with an EOT of 1.3 nm and j = 0.02 Acm<sup>-2</sup>, in line with ITRS LSTP targets for the 22 nm node [49]. This stack can be optimized further for scaling requirements beyond the 22 nm node as GdSiO has been successfully introduced into fully functional SOI n-MOSFETs with TiN metal gate electrodes [74].

# 3.2.1. Thermal Stability and Mechanism of GdSiO Formation

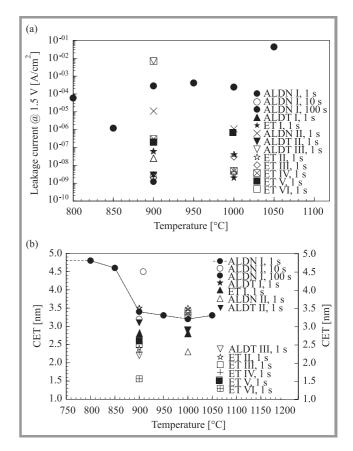

The thermal behavior of these Gd<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate stacks can be assessed by plotting MIS device leakage current and CET versus RTA process temperature as shown in Fig. 3(a) and Fig. 3(b), respectively. It can be seen that very low leakage currents ( $< 10^{-7}$  A/cm<sup>2</sup>) are obtained for stacks deposited by both techniques (evaporation and ALD), in particular when there is a thermal oxide as an IL. Furthermore, an increase from 900°C to 1000°C does not compromise the leakage current; it is further reduced. The observed trend is a significant reduction of the capacitance equivalent thickness after annealing as outlined in Fig. 3(b). When observing the RTA time series, very low leakage currents of  $\sim 10^{-9}$  A/cm<sup>2</sup> were obtained for 10 s and 100 s anneal time (Fig. 3(a)), however the CET is largely increased after 100 s anneal (Fig. 3(b)). The CET is reduced further when anneal time varies from 1 to 10 s.

Oxygen has been found to diffuse into the film eliminating oxygen vacancies, but Si diffusion was absent after oxygen and vacuum annealing at temperatures up to 800°C for GdSiO films on Si(100) [75]. It has been suggested [23] that silicate formation for rare earth based materials occurs through inter-diffusion with underlying SiO<sub>2</sub> to form silicates, rather than by diffusion of Si and subsequent oxidation, as this can explain absence of silicates when capped structures are used [76]-[78]. It seems that excluding oxygen and preventing the oxidation of the silicon substrate can prevent silicate formation. There are also reports on GdSiO gate dielectric films deposited on Si(001) substrates using UHV (ultra high-vacuum) e-beam evaporation from pressed-powder targets [24]. These films were amorphous as deposited and remained amorphous when annealed to temperatures up to 900°C, and showed  $k \sim 16$  and low leakage currents of  $5.7 \cdot 10^{-3}$  A/cm<sup>2</sup> at 1 V.

*Fig. 3.* (a) Leakage current and (b) CET versus anneal temperature for various  $Gd_2O_3/SiO_2$  gate stacks deposited by ALD and e-beam evaporation.

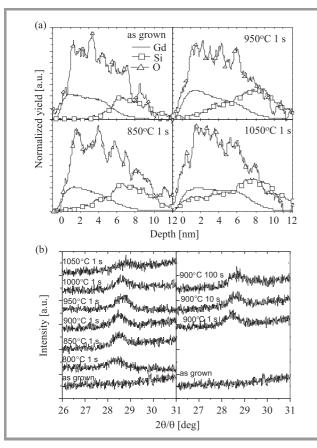

For the ALD Gd<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate stacks discussed here, annealing causes substantial reordering of the layers and the effects are apparent by plotting the MEIS energy spectra as depth profiles for Gd, Si and O shown in Fig. 4(a). It can be seen that higher temperatures drive more silicon into the high-k layer. The source of the incorporated Si is likely to be from inter-diffusion with the native SiO<sub>2</sub> layer, with some contribution from the substrate [65]. Diffraction patterns (XRD) from samples annealed in the temperature range from 800-1050°C contain a peak at 28.6° referring to cubic Gd<sub>2</sub>O<sub>3</sub>. The most pronounced peaks, corresponding to the highest level of crystallinity in the films, occur around 900°C to 950°C. The MEIS and XRD results suggest that two competing mechanisms occur during annealing [65]. The ALD  $Gd_2O_3$  layer crystallizes into the cubic phase at all temperatures studied and the extent of crystallinity increases with increasing temperature. The second mechanism is the diffusion of Si into the layer. As Si is swept into the polycrystalline  $Gd_2O_3$  the crystalline grains become amorphised. This reduces the thickness of the crystalline layer and thus the intensity of the XRD diffraction features. Crystallisation dominates at lower temperatures and silicate formation dominates at higher temperatures. It follows that the final state of a film after annealing depends on the film thickness as well as the anneal temperature and duration, as expected for a diffusion driven process [23].

*Fig. 4.* (a) MEIS and (b) XRD profiles for ALD grown  $Gd_2O_3/SiO_2$  gate stacks under different RTA conditions [65].

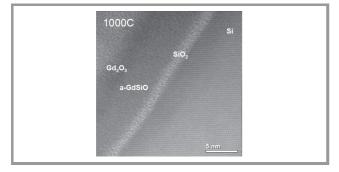

Fig. 5. HRTEM image of ALD bi-layer structure  $Gd_2O_3/GdSiO/SiO_2$  after RTA at 1000°C for 1 s in N<sub>2</sub>.

Figure 5 depicts the case when, even after 1000°C anneal, the layer is not fully transformed into the silicate but contains bi-layer structure due to the initially deposited thicker ( $\sim 8 \text{ nm}$ ) Gd<sub>2</sub>O<sub>3</sub> film. Note also that the interfacial SiO<sub>2</sub> layer is present after the anneal. Similar has been observed for other RE based silicates [23], [50], [52].

#### 3.2.2. Band Offsets for GdSiO

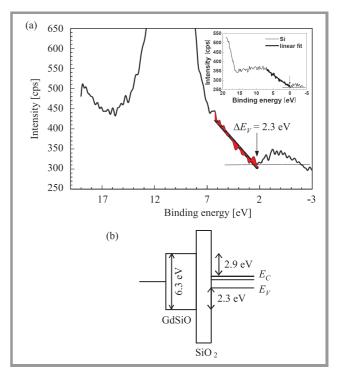

An insight into the energy band line-ups of ALD GdSiO gate stacks is provided by XPS measurements. The onset of the excitation from the valence to conduction bands can be observed at an energy corresponding to the band gap energy below the XPS O 1 s core signal [79], [80]. From the threshold energy of an energy loss spectrum for O 1 s

56

photoelectrons, the bandgap of GdSiO is determined to be 6.3 eV [81]. The measured XPS valence band spectrum for GdSiO/SiO<sub>2</sub>/Si is shown in Fig. 6(a). The valence band offset between GdSiO and Si is determined by evaluating the energies of the valence band maxima of GdSiO and Si. These energies were determined by analytically finding the intersection of the regression-determined line segment defining the leading edge of the valence band and the flat energy distribution curve [82], and taking into account charging effects on the XPS spectra [83], [84].

*Fig. 6.* (a) The XPS valence band spectrum and (b) the band diagram of ALD GdSiO<sub>2</sub>/Si(100) structure.

The values of 2.31 eV for GdSiO and 0.01 eV for Si(100) are estimated. The difference of these values corresponds to a valence band offset of 2.3 eV. Thus the conduction band offset is 2.9 eV. The resulting energy band alignment for a GdSiO/SiO<sub>2</sub>/Si(100) is shown in Fig. 6(b). The results are comparable to the ones published by Hattori *et al.* [85] for Gd<sub>2</sub>O<sub>3</sub>/silicate/SiO<sub>2</sub>/Si, where  $E_g = 6.4$  eV,  $\Delta E_V = 2.2$  eV and  $\Delta E_C = 3.1$  eV. For advanced CMOS application, the band offsets to Si above 2 eV and roughly equal ( $\Delta E_C \approx \Delta E_V$ ) represent one of the most desirable features for future gate stack.

# 4. Beyond the 22 nm Node

Recent reports indicate that lanthanum-based ternary oxides are likely to have major role in meeting the ITRS requirements for scaling beyond the 22 nm node [86]. The growth methods proposed include molecular beam deposition (MBD) [87], [88], pulsed laser deposition (PLD) [89], or ALD [90]. The interfacial layers can be avoided when

ternary rare earth oxide films (La<sub>x</sub>M<sub>2-x</sub>O<sub>3</sub>, M = Sc, Lu, or Y) are deposited on Si by ALD from metal amidinate precursors and H<sub>2</sub>O [86]. Both LaScO<sub>3</sub> and LaLuO<sub>3</sub> films are found to be amorphous and free of interfacial layers, with high dielectric constants ( $\sim 23$  for LaScO<sub>3</sub> and  $28 \pm 1$ for LaLuO<sub>3</sub>), low leakage current density, and are scalable to EOT < 1 nm.  $La_{1.23}Y_{0.77}O_3$  films have polycrystalline structures with moderately high  $k = 17 \pm 1.3$  and low leakage current [86]. The growth of stoichiometric and smooth LaLuO<sub>3</sub> films ( $C_E \sim 65$  eV) that remain amorphous up to 1000°C has been reported [89]. The band gap has been found to be  $5.2 \pm 0.1$  eV, with symmetrical conduction and valence band offsets of 2.1 eV, a dielectric constant of  $\sim$  32, and low leakage current density levels. Amorphous GdScO<sub>3</sub> films have also demonstrated a high permittivity of 22, the EOT of  $\sim 1$  nm, and the leakage current density less than 2 mA/cm<sup>2</sup> [91].

LaAlO<sub>3</sub>-based heterostructures are also expected to fulfil the requirements of ITRS beyond 22 nm [92]. Very aggressive scaling < 1 nm EOT with reasonable leakage currents can be achieved for amorphous LaAlO<sub>3</sub> (LAO) films on Si(001), but interfacial SiO<sub>2</sub> grows at anneals above 400°C. The addition of an Al<sub>2</sub>O<sub>3</sub> interlayer increases the thermal stability up to 600°C. Both a-LaAlO<sub>3</sub>/Si(001) and a-LaAlO<sub>3</sub>/ $\gamma$ -Al<sub>2</sub>O<sub>3</sub>/Si(001) systems should be appropriate for gate-first processes, when optimized. Suzuki *et al.* at Toshiba Labs have reported [93] 0.3 nm EOT for amorphous LaAlO<sub>3</sub> grown by PLD. It should be noted that LAO often exhibits structural instability and interface reaction during high temperature treatment [94], [95].

There are few publications about ultra-thin high-*k* films with EOTs lower than 1 nm on crystalline Gd<sub>2</sub>O<sub>3</sub> grown by MBE [62], [72]. There has been a recent attempt to grow epitaxially ternary  $(Nd_{1-x}Gd_x)_2O_3$  (NGO) thin films, with the idea that a combination of Gd<sub>2</sub>O<sub>3</sub> and Nd<sub>2</sub>O<sub>3</sub> would create a system exhibiting exact lattice matching with Si [96]. The NGO films show promising electrical features, the CET of 0.9 nm and leakage currents below 1 mA/cm<sup>2</sup>. The key parameter for IL control is found to be oxygen partial pressure during the interface formation and/or MBE growth; it prevents silicide inclusions, while avoiding the formation of interfacial SiO<sub>x</sub> [63], [71]. GdSiO material, grown by e-beam evaporation or ALD, as discussed in this paper, has potential for further scaling and is also contender as a high-*k* material beyond the 22 nm node.

Although there seem to be several possibilities to engineer the gate stack for ultimate scaling, most of the high-*k* materials reported above show high mid-gap density of interface states ( $D_{it} = 3 \cdot 10^{11} \text{ eV}^{-1}\text{cm}^{-2}$  [91],  $1.4 \cdot 10^{12} \text{ eV}^{-1}\text{cm}^{-2}$  [96],  $5 \cdot 10^{12} \text{ eV}^{-1}\text{cm}^{-2}$  [95]), and bulk fixed charge density  $> 10^{11} \text{ cm}^{-2}$  [91], [96]. On the pathway of scaling, it is critical to obtain an optimal high-*k*-Si interface with acceptably low  $D_{it} < 10^{11} \text{ eV}^{-1}\text{cm}^{-2}$  and mobility in MOSFET channels approaching the universal curve. At the same time, the problem of reliability and stability (charge trapping) [97], [98] of these new dielectrics still remains acute and requires further studies.

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY 4/2009 5. Summary

In this paper, recent work on rare earth based oxides and silicates has been reviewed with an emphasis on materials suitable for integration according to the ITRS LSTP targets for the 22 nm node and beyond. Understanding the mechanisms that create interfacial layers is a key requirement for further scaling of these high-k dielectrics. There are several approaches to achieve elimination of the interfacial SiO<sub>2</sub> layer and thus ultimate scaling, employed by various research labs worldwide. Reaction of the SiO<sub>2</sub> with a RE oxide causes an effective increase for the k-value of the interfacial layer. Furthermore, full reaction of the interfacial layer with cap can be used to form a higher-k dielectric, or the formation of epitaxial high-k dielectrics can be utilised. The scaling potential of GdSiO-based gate stacks which exhibit excellent thermal stability, low leakage currents and sufficiently high band offsets to be employed in the devices for technological nodes beyond 22 nm has been demonstrated.

## Acknowledgements

The authors collaborate under the banner of the high-*k* gang (http://www.high-k-gang.eu/). The work has benefited from funding provided by the EC PULLNANO (Academic Cluster), the Network of Excellence NANOSIL and EPSRC, UK. The authors are part of the SINANO Institute.

### References

- [1] S. Natarajan, M. Armstrong, M. Bost, R. Brain, and M. Brazier, "A 32 nm logic technology featuring 2nd generation high-k metalgate transistors, enhanced channel strain and 0.171 μ m<sup>2</sup> SRAM cell size in a 291 Mb array", in *Proc. IEEE IEDM 2008 Conf.*, San Francisco, USA, 2008, pp. 941–943.

- [2] H. S. Yang *et al.*, "Scaling of 32 nm low power SRAM with high-k metal gate", in *Proc. IEEE IEDM 2008 Conf.*, San Francisco, USA, 2008, pp. 233–236.

- [3] H. Kawasaki *et al.*, "Demonstration of highly scaled FinFET SRAM cells with high-*k*/metal gate and investigation of characteristic variability for the 32 nm node and beyond", in *Proc. IEEE IEDM 2008 Conf.*, San Francisco, USA, 2008, pp. 237–240.

- [4] C. H. Diaz *et al.*, "32 nm gate-first high-k/metal-gate technology for high performance low power applications", in *Proc. IEEE IEDM Tech. Dig.*, San Francisco, USA, 2008, pp. 629–632.

- [5] S. Hasegawa *et al.*, "A cost-conscious 32 nm CMOS platform technology with advanced single exposure lithography and gate-first metal gate/high-*k* process", in *Proc. IEEE IEDM 2008 Conf.*, San Francisco, USA, 2008, pp. 938–940.

- [6] K. Mistry *et al.*, "A 45 nm logic technology with high-k+ metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging", in *Proc. IEEE IEDM Tech. Dig.*, Washington, USA, 2007, pp. 247–250.

- [7] S. Mayuzumi, S. Yamakawa, Y. Tateshita, T. Hirano, M. Nakata, S. Yamaguchi, K. Tai, H. Wakabayashi, M. Tsukamoto, and N. Nagashima, "High-performance metal/high-k n- and p-MOSFETs with top-cut dual stress liners using gate-last damascene process on (100) substrates", *IEEE Trans. Electron Dev.*, vol. 56, no. 4, pp. 620–626, 2009.

- [8] X. Chen *et al.*, "A cost effective 32 nm high-k/metal gate CMOS technology for low power applications with single-metal/gate-first process", in *Proc. IEEE VLSI Tech. Symp.*, Honolulu, Hawaii, USA, 2008, pp. 88–89.

- [9] M. Chudzik *et al.*, "High-performance high-k metal gates for 45 nm CMOS and beyond with gate-first processing", in *Proc. IEEE VLSI Tech. Symp.*, Kyoto, Japan, 2007, pp. 194–195.

- [10] S. Tyagi *et al.*, "Future device scaling beyond traditional CMOS", in *Proc. IEDST'09 Conf.*, Mumbai, India, 2009, pp. 1–4.

- [11] "International Technology Roadmap for Semiconductors (ITRS)"[Online]. Available: http://public.itrs.net

- [12] H. J. Osten, "Epitaxial high-k dielectrics on silicon", in Proc. IEEE ASDAM 2004 Conf., Smolenice, Slovakia, 2004, pp. 155–162.

- [13] Y. Ma, Y. Ono, L. Stecker, D. R. Evans, and S. T. Hsu, "Zirconium oxide based gate dielectrics with equivalent oxide thickness of less than 1.0 nm and performance of submicron MOSFET using a nitride gate replacement process", in *Proc. IEEE IEDM Conf.*, Washington, USA, 1999, pp. 149–152.

- [14] B. H. Lee, L. Kang, W.-J. Qi, R. Nieh, Y. Jeon, K. Onishi, and J. C. Lee, "Ultrathin hafnium oxide with low leakage and excellent reliability for alternative gate dielectric application", in *Proc. IEEE IEDM Conf.*, Washington, USA, 1999, pp. 133–136.

- [15] S. Jeon, C.-J. Choi, T.-Y. Seong, and H. Hwang, "Electrical characteristics of ZrO<sub>x</sub>N<sub>y</sub> prepared by NH<sub>3</sub> annealing of ZrO<sub>2</sub>", *Appl. Phys. Lett.*, vol. 79, iss. 2, pp. 245–247, 2001.

- [16] J. Kwo et al., "Properties of high k gate dielectrics Gd<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> for Si", J. Appl. Phys., vol. 89, iss. 7, pp. 3920–3927, 2001.

- [17] O. Engstrom, B. Raeissi, S. Hall, O. Buiu, M. C. Lemme, H. D. B. Gottlob, P. K. Hurley, and K. Cherkaoui, "Navigation aids in the search for future future high-*k* dielectrics: physical and electrical trends", *Solid-State Electron.*, vol. 51, iss. 4, pp. 622–626, 2007.

- [18] J. Robertson, "High dielectric constant oxides", Eur. Phys. J. Appl. Phys., vol. 28, no. 3, pp. 265–291, 2004.

- [19] L. Pantisano, T. Schram, B. O'Sullivan, T. Conard, S. De Gendt, G. Groeseneken, P. Zimmerman, A. Akheyar, M. M. Heyns, S. Shamuilla, V. V. Afanas'ev, and A. Stesmans, "Effective work function modulation by controlled dielectric monolayer deposition", *Appl. Phys. Lett.*, vol. 89, iss. 11, pp. 113505-1–113505-3, 2006.

- [20] L.-A. Ragnarsson, V. S. Chang, H. Y. Yu, H.-J. Cho, T. Conard, K. M. Yin, A. Delabie, J. Swerts, T. Schram, S. De Gendt, and S. Biesemans, "Achieving conduction band-edge effective work functions by La<sub>2</sub>O<sub>3</sub> capping of hafnium silicates", *IEEE Electron Dev. Lett.*, vol. 28, no. 6, pp. 486–488, 2007.

- [21] G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-k gate dielectrics: current status and materials properties considerations", *J. Appl. Phys.*, vol. 89, iss. 10, pp. 5243–5275, 2001.

- [22] I. Z. Mitrovic, O. Buiu, S. Hall, C. Bungey, T. Wagner, W. Davey, and Y. Lu, "Electrical and structural properties of hafnium silicate thin films", *Microelectron. Reliab.*, vol. 47, iss. 4–5, pp. 645–648, 2007.

- [23] S. Van Elshocht, C. Adelmann, T. Conard, A. Delabie, A. Franquet, L. Nyns, O. Richard, P. Lehnen, J. Swerts, and S. De Gendt, "Silicate formation and thermal stability of ternary rare earth oxides as high-*k* dielectrics", *J. Vac. Sci. Technol. A*, vol. 26, no. 4, pp. 724–730, 2008.

- [24] J. A. Gupta, D. Landheer, J. P. McCaffrey, and G. I. Sproule, "Gadolinium silicate gate dielectric films with sub-1.5 nm equivalent oxide thickness", *Appl. Phys. Lett.*, vol. 78, iss. 12, pp. 1718–1720, 2001.

- [25] M. Copel, E. Cartier, and F. M. Ross, "Formation of a stratified lanthanum silicate dielectric by reaction with Si(001)", *Appl. Phys. Lett.*, vol. 78, iss. 11, pp. 1607–1609, 2001.

- [26] G. Lupina, T. Schroeder, C. Wenger, J. Dabrowski, and H.-J. Müssig, "Thermal stability of Pr silicate high-k layers on Si(001)", *Appl. Phys. Lett.*, vol. 89, iss. 22, pp. 222909-1–222909-3, 2006.

- [27] A. Sakai, S. Sakashita, M. Sakashita, Y. Yasuda, S. Zaima, and S. Miyazaki, "Praseodymium silicate formed by postdeposition high-temperature annealing", *Appl. Phys. Lett.*, vol. 85, no. 22, pp. 5322–5324, 2004.

- [28] H. Iwai, S. Ohmi, S. Akama, C. Ohshima, A. Kikuchi, I. Kashiwagi, J. Taguchi, H. Yamamoto, J. Tonotani, Y. Kim, I. Ueda, A. Kuriyama, and Y. Yoshihara, "Advanced gate dielectric materials for sub-100 nm CMOS", in *Proc. IEEE IEDM Conf.*, San Francisco, USA, 2002, pp. 625–628.

- [29] D. P. Norton, "Synthesis and properties of epitaxial electronic oxide thin-film materials", *Mater. Sci. Eng. R*, vol. 43, iss. 5–6, pp. 139–247, 2004.

- [30] P. Delugas and V. Fiorentini, "Dielectric properties of two phases of crystalline lutetium oxide", *Microelectron. Reliab.*, vol. 45, iss. 5–6, pp. 831–833, 2005.

- [31] H. Ono and T. Katsumata, "Interfacial reactions between thin rareearth-metal oxide films and Si substrates", *Appl. Phys. Lett.*, vol. 78, no. 13, pp. 1832–1834, 2001.

- [32] J. Wu, M. Y. Yang, A. Chin, W. J. Chen, and C. M. Kwei, "Electrical characteristics of high quality La<sub>2</sub>O<sub>3</sub> gate dielectric with equivalent oxide thickness of 5 Å", *IEEE Electron. Dev. Lett.*, vol. 21, no. 7, pp. 341–343, 2000.

- [33] J.-B. Cheng, A.-D. Li, Q.-Y. Shao, H.-Q. Ling, D. Wu, Y. Wang, Y.-J. Bao, M. Wang, Z.-G. Liu, and N.-B. Ming, "Growth and characteristics of La<sub>2</sub>O<sub>3</sub> gate dielectric prepared by low pressure metalorganic chemical vapor deposition", *Appl. Surf. Sci.*, vol. 233, iss. 1–4, pp. 91–98, 2004.

- [34] H. J. Osten, J. P. Liu, and H. J. Mussig, "Band gap and band discontinuities at crystalline Pr<sub>2</sub>O<sub>3</sub>/Si(001) heterojunctions", *Appl. Phys. Lett.*, vol. 80, iss. 2, pp. 297–299, 2002.

- [35] R. Lo Nigro, V. Raineri, C. Bongiorno, R. Toro, G. Malandrino, and I. L. Fragala, "Dielectric properties of Pr<sub>2</sub>O<sub>3</sub> high-*k* films grown by metalorganic chemical vapor deposition on silicon", *Appl. Phys. Lett.*, vol. 83, iss. 1, pp. 129–131, 2003.

- [36] R. Lo Nigro, R. G. Toro, G. Malandrino, V. Raineri, and I. L. Fragala, "A simple route to the synthesis of Pr<sub>2</sub>O<sub>3</sub> high-*k* thin films", *Adv. Mater.*, vol. 15, iss. 13, pp. 1071–1075, 2003.

- [37] T.-M. Pan, F.-J. Tsai, C.-I. Hsieh, and T.-W. Wu, "Structural properties and electrical characteristics of praseodymium oxide gate dielectrics", *Electrochem. Solid-State Lett.*, vol. 10, no. 4, pp. G21–G24, 2007.

- [38] J. Kwo et al., "High ε gate dielectrics Gd<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> for silicon", Appl. Phys. Lett., vol. 77, iss. 1, pp. 130–132, 2000.

- [39] M. D. Kannan, S. K. Narayandass, C. Balasubramanian, and D. Mangalaraj, "Structure and electrical properties of thermally evaporated Nd<sub>2</sub>O<sub>3</sub> thin films", *Phys. Stat. Sol. A*, vol. 128, iss. 2, pp. 427–433, 1991.

- [40] A. Fissel, Z. Elassar, O. Kirfel, E. Bugiel, M. Czernohorsky, and H. J. Osten, "Interface formation during molecular beam epitaxial growth of neodymium oxide on silicon", *J. Appl. Phys.*, vol. 99, iss. 7, pp. 074105-1–074105-6, 2006.

- [41] T. Busani and R. A. B. Devine, "The importance of network structure in high-k dielectrics: LaAlO<sub>3</sub>, Pr<sub>2</sub>O<sub>3</sub> and Ta<sub>2</sub>O<sub>5</sub>", J. Appl. Phys., vol. 98, iss. 4, pp. 044102-1–044102-5, 2005.

- [42] K. J. Hubbart and D. G. Schlom, "Thermodynamic stability of binary oxides in contact with silicon", J. Mater. Res., vol. 11, no. 11, pp. 2757–2776, 1996.

- [43] M. Copel, E. Cartier, V. Narayanan, M. C. Reuter, S. Guha, and N. Bojarczuk, "Characterization of silicate/Si(001) interfaces", *Appl. Phys. Lett.*, vol. 81, iss. 22, pp. 4227–4229, 2002.

- [44] C.-J. Choi, M.-G. Jang, Y.-Y. Kim, M.-S. Jun, T.-Y. Kim, and M.-H. Song, "Electrical and structural properties of high-k Er-silicate gate dielectric formed by interfacial reaction between Er and SiO<sub>2</sub> films", *Appl. Phys. Lett.*, vol. 91, iss. 1, pp. 012903-1–012903-3, 2007.

- [45] G. Lupina, T. Schroeder, J. Dabrowski, C. Wenger, A. U. Mane, H.-J. Mussig, P. Hoffmann, and D. Schmeisser, "Praseodymium silicate films on S(100) for gate dielectric applications: physical and electrical characterization", *J. Appl. Phys.*, vol. 99, iss. 11, pp. 114109-1–114109-5, 2006.

- [46] M. Copel, "Selective desorption of interfacial SiO<sub>2</sub>", *Appl. Phys. Lett.*, vol. 82, iss. 10, pp. 1580–1582, 2003.

- [47] D. J. Lichtenwalner *et al.*, "Lanthanum silicate gate dielectric stacks with subnanometer equivalent oxide thickness utilizing an interfacial silica consumption reaction", *J. Appl. Phys.*, vol. 98, iss. 2, pp. 024314-1–024314-6, 2005.

- [48] A. Laha, A. Fissel, and H. J. Osten, "Engineering the interface between epitaxial lanthanide oxide thin films and Si substrates: a route towards tuning the electrical properties", *Microelectron. Eng.*, vol. 84, iss. 9–10, pp. 2282–2285, 2007.

- [49] H. D. B. Gottlob, M. Schmidt, A. Stefani, M. C. Lemme, H. Kurz, I. Z. Mitrovic, W. M. Davey, S. Hall, M. Werner, P. R. Chalker, K. Cherkaoui, P. K. Hurley, J. Piscator, O. Engstrom, and S. B. Newcomb, "Scaling potential and MOSFET integration of thermally stable Gd silicate dielectrics", *Microelectron. Eng.*, vol. 86, iss. 7–9, pp. 1642–1645, 2009.

- [50] H. D. B. Gottlob, M. Schmidt, M. C. Lemme, H. Kurz, I. Z. Mitrovic, M. Werner, W. M. Davey, S. Hall, P. R. Chalker, K. Cherkaoui, P. K. Hurley, B. Raeissi, O. Engstrom, and S. B. Newcomb, "Gd silicate: a high-k dielectric compatible with high temperature annealing", J. Vac. Sci. Technol. B, vol. 27, no. 1, pp. 249–252, 2009.

- [51] D. Eom, S. Y. No, C. S. Hwang, and H. J. Kim, "Deposition characteristics and annealing effect of La<sub>2</sub>O<sub>3</sub> films prepared using La(iPrCp)<sub>3</sub> precursor", *J. Electrochem. Soc.*, vol. 154, iss. 3, pp. G49–G53, 2007.

- [52] X. Wu, D. Landheer, G. I. Sproule, T. Quance, M. J. Graham, and G. A. Botton, "Characterization of gadolinium and lanthanum oxide films on Si (100)", *J. Vac. Sci. Technol. A*, vol. 20, no. 3, pp. 1141–1144, 2002.

- [53] S. Guha, E. Cartier, M. A. Gribelyuk, N. A. Bojarczuk, and M. C. Copel, "Atomic beam deposition of lanthanum- and yttriumbased oxide thin films for gate dielectrics", *Appl. Phys. Lett.*, vol. 77, iss. 17, pp. 2710–2712, 2000.

- [54] A. C. Jones, "Molecular design of improved precursors for the MOCVD of electroceramic oxides", J. Mater. Chem., vol. 12, no. 9, pp. 2576–2590, 2002.

- [55] A. C. Jones, H. C. Aspinall, P. R. Chalker, R. J. Potter, K. Kukli, A. Rahtu, M. Ritala, and M. Leskala, "Recent developments in the MOCVD and ALD of rare earth oxides and silicates", *Mater. Sci. Eng. B*, vol. 118, iss. 1–3, pp. 97–104, 2005.

- [56] R. Lupták, K. Fröhlich, A. Rosová, K. Hušeková, M. Tapajna, D. Machajdík, M. Jergel, J. P. Espinós, and C. Mansilla, "Growth of gadolinium oxide films for advanced MOS structure", *Microelectron. Eng.*, vol. 80, pp. 154–157, 2005.

- [57] M. P. Singh, C. S. Thakur, K. Shalini, S. Banerjee, N. Bhat, and S. A. Shivashankar, "Structural, optical, and electrical characterization of gadolinium oxide films deposited by low-pressure metalorganic chemical vapour deposition", *J. Appl. Phys.*, vol. 96, no. 10, pp. 5631–5637, 2004.

- [58] B. A. Orlowski, E. Guziewicz, N. E. Orlowska, A. Bukowski, and R. L. Johnson, "Photoemission study of Gd on clean Si(111) surface", *Surf. Sci.*, vol. 507–510, pp. 218–222, 2002.

- [59] P. Y. Kuei and C. C. Hu, "Gadolinium oxide high-k gate dielectrics prepared by anodic oxidation", *Appl. Surf. Sci.*, vol. 254, iss. 17, pp. 5487–5491, 2008.

- [60] H.-H. Ko, L.-B. Chang, M.-J. Jeng, P.-Y. Kuei, and K.-Y. Horng, "Properties of thermal gadolinium oxide films on silicon", *Jap. J. Appl. Phys.*, vol. 44, no. 5A, pp. 3205–3208, 2005.

- [61] L.-Z. Hsieh, H.-H. Ko, P.-Y. Kuei, L.-B. Chang, and M.-J. Jeng, "Hysteresis in gadolinium oxide metal-oxide-semiconductor capacitors", J. Appl. Phys., vol. 98, iss. 7, pp. 076110-1–076110-3, 2005.

- [62] A. Laha, H. J. Osten, and A. Fissel, "Influence of interface layer composition on the electrical properties of epitaxial Gd<sub>2</sub>O<sub>3</sub> thin films for high-*k* application", *Appl. Phys. Lett.*, vol. 90, iss. 11, pp. 113508-1–113508-3, 2007.

- [63] M. Czernohorsky, E. Bugiel, H. J. Osten, A. Fissel, and O. Kirfel, "Impact of oxygen supply during growth on the electrical properties of crystalline Gd<sub>2</sub>O<sub>3</sub> thin films on Si(001)", *Appl. Phys. Lett.*, vol. 88, iss. 15, pp. 152905-1–152905-3, 2006.

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY 4/200

- [64] I. Z. Mitrovic, M. Werner, W. M. Davey, S. Hall, P. R. Chalker, H. D. B. Gottlob, M. C. Lemme, O. Engstrom, K. Cherkaoui, and P. K. Hurley, "Quest for an optimal gadolinium silicate gate dielectric stack", in *39th Conf. IEEE SISC 2008*, San Diego, USA, 2008.

- [65] M. Werner, P. R. Chalker, W. M. Davey, I. Z. Mitrovic, S. Hall, and I. Alexandrou, "Formation of high-k gadolinium silicate via silicon oxide inter-diffusion into gadolinium oxide", *Appl. Phys. Lett.*, 2009 (submitted).

- [66] J. W. Johnson *et al.*, "Gd<sub>2</sub>O<sub>3</sub>/GaN metal-oxide-semiconductor fieldeffect transistor", *Appl. Phys. Lett.*, vol. 77, iss. 20, pp. 3230–3232, 2000.

- [67] M. Hong *et al.*, "Single-crystal GaN/Gd<sub>2</sub>O<sub>3</sub>/GaN heterostructure", *J. Vac. Sci. Technol. B*, vol. 20, iss. 3, pp. 1274–1277, 2002.

- [68] M. Hong, M. Passlack, J. P. Mannaerts, J. Kwo, S. N. G. Chu, N. Moriya, S. Y. Hou, and V. J. Fratello, "Low interface state density oxide-GaAs structures fabricated by in situ molecular beam epitaxy", *J. Vac. Sci. Technol. B*, vol. 14, iss. 3, pp. 2297–2300, 1996.

- [69] M. Hong, J. Kwo, A. R. Kortan, J. P. Mannaerts, and A. M. Sergent, "Epitaxial cubic gadolinium oxide as a dielectric for gallium arsenide passivation", *Science*, vol. 283, no. 5409, pp. 1897–1900, 1999.

- [70] D. Jia, L. Lu, and W. M. Yu, "Erbium energy levels relative to the band gap of gadolinium oxide", *Opt. Commun.*, vol. 212, iss. 1–3, pp. 97–100, 2002.

- [71] A. Fissel, M. Czernohorsky, and H. J. Osten, "Characterization of crystalline rare-earth oxide high-k dielectrics grown by molecular beam epitaxy on silicon carbide", J. Vac. Sci. Technol. B, vol. 24, no. 4, pp. 2115–2118, 2006.

- [72] H. D. B. Gottlob *et al.*, "0.86-nm CET gate stacks with epitaxial Gd<sub>2</sub>O<sub>3</sub> high-*k* dielectrics and FUSI NiSi metal electrodes", *IEEE Electron Dev. Lett.*, vol. 27, no. 10, pp. 814–816, 2006.

- [73] M. Czernohorsky, D. Tetzlaff, E. Bugiel, R. Dargis, H. J. Osten, H. D. B. Gottlob, M. Schmidt, M. C. Lemme, and H. Kurz, "Stability of crystalline Gd<sub>2</sub>O<sub>3</sub> thin films on silicon during rapid thermal annealing", *Semicond. Sci. Technol.*, vol. 23, no. 3, pp. 035010-1–035010-4, 2008.

- [74] M. Schmidt, A. Stefani, H. D. B. Gottlob, and H. Kurz, "Integration of Gd silicate/TiN gate stacks into SOI n-MOSFETs", *Microelectron. Eng.*, vol. 86, iss. 7–9, pp. 1683–1685, 2009.

- [75] D. Landheer, X. Wu, J. Morais, I. J. R. Baumvol, R. P. Pezzi, L. Miotti, W. N. Lennard, and J. K. Kim, "Thermal stability and diffusion in gadolinium silicate gate dielectric films", *Appl. Phys. Lett.*, vol. 79, no. 16, pp. 2618–2620, 2001.

- [76] B. W. Busch, J. Kwo, M. Hong, J. P. Mannaerts, B. J. Sapjeta, W. H. Schulte, E. Garfunkel, and T. Gustafsson, "Interface reactions of high-k Y<sub>2</sub>O<sub>3</sub> gate oxides with Si", *Appl. Phys. Lett.*, vol. 79, iss. 15, pp. 2447–2449, 2001.

- [77] D. Niu, R. W. Ashcraft, and G. N. Parsons, "Water absorption and interface reactivity of yttrium oxide gate dielectrics on silicon", *Appl. Phys. Lett.*, vol. 80, iss. 19, pp. 3575–3577, 2002.

- [78] A. Goryachko, J. P. Liu, D. Krüger, H. J. Osten, E. Bugiel, R. Kurps, and V. Melnik, "Thermal stability of Pr<sub>2</sub>O<sub>3</sub> films grown on Si(100) substrate", *J. Vac. Sci. Technol. A*, vol. 20, iss. 6, pp. 1860–1866, 2002.

- [79] S. Miyazaki, H. Nishimura, M. Fukuda, L. Ley, and J. Ristein, "Structure and electronic states of ultrathin SiO<sub>2</sub> thermally grown on Si(100) and Si(111) surfaces", *Appl. Surf. Sci.*, vol. 113–114, pp. 585–589, 1997.

- [80] S. Miyazaki, "Characterization of high-k gate dielectric/silicon interfaces", Appl. Surf. Sci., vol. 190, iss. 1–4, pp. 66–74, 2002.

- [81] I. Z. Mitrovic *et al.*, "Shift in the band-offsets and dominant trap levels in Gd-based high-k gate stacks", J. Appl. Phys., 2009 (in preparation).

- [82] A. Fissel, J. Dabrowski, and H. J. Osten, "Photoemission and ab initio theoretical study of interface and film formation during epitaxial growth and annealing of praseodymium oxide on Si(001)", J. Appl. Phys., vol. 91, iss. 11, pp. 8986–8991, 2002.

- [83] S. Toyoda *et al.*, "Precise determination of band offsets and chemical states in SiN/Si studied by photoemission spectroscopy and x-ray absorption spectroscopy", *Appl. Phys. Lett.*, vol. 87, iss. 10, pp. 102901-1–102901-3, 2005.

- [84] Y. Liu, T. P. Chen, L. Ding, S. Zhang, Y. Q. Fu, and S. Fung, "Charging mechanism in a SiO<sub>2</sub> matrix embedded with Si nanocrystals", *J. Appl. Phys.*, vol. 100, iss. 9, pp. 096111-1–096111-3, 2006.

- [85] T. Hattori, T. Yoshida, T. Shiraishi, K. Takahashi, H. Nohira, S. Joumori, K. Nakajima, M. Suzuki, K. Kimura, I. Kashiwagi, C. Ohshima, S. Ohmi, and H. Iwai, "Composition, chemical structure, and electronic band structure of rare earth oxide/Si(100) interfacial transition layer", *Microelectron. Eng.*, vol. 72, iss. 1–4, pp. 283–287, 2004.

- [86] H. Wang, J.-J. Wang, R. Gordon, J.-S. M. Lehn, H. Li, D. Hong, and D. V. Shenai, "Atomic layer deposition of lanthanum-based ternary oxides", *Electrochem. Solid-State Lett.*, vol. 12, no. 4, pp. G13–G15, 2009.

- [87] J. M. J. Lopes, U. Littmark, M. Roeckerath, S. Lenk, J. Schubert, and S. Mantl, "Effects of annealing on the electrical and interfacial properties of amorphous lanthanum scandate high-k films prepared by molecular beam deposition", *J. Appl. Phys.*, vol. 101, iss. 10, pp. 104109-1–104109-5, 2007.

- [88] J. M. J. Lopes, M. Roeckerath, T. Heeg, U. Littmark, J. Schubert, S. Mantl, Y. Jia, and D. G. Schlom, "La-based ternary rare-earth oxides as alternative high-k dielectrics", *Microelectron. Eng.*, vol. 84, iss. 9–10, pp. 1890–1893, 2007.

- [89] J. M. J. Lopes *et al.*, "Amorphous lanthanum lutetium oxide thin films as an alternative high-*k* gate dielectric", *Appl. Phys. Lett.*, vol. 89, iss. 22, pp. 222902-1–222902-3, 2006.

- [90] J. M. J. Lopes, M. Roeckerath, T. Heeg, J. Schubert, S. Mantl, and V. V. Afanas'ev, "Amorphous lantahnum lutetium oxide thin films as an alternative high-*k* material", *ECS Trans.*, vol. 11, no. 4, pp. 311–318, 2007.

- [91] K. H. Kim, D. B. Farmer, J.-S. M. Lehn, P. V. Rao, and R. G. Gordon, "Atomic layer deposition of gadolinium scandate films with high dielectric constant and low leakage current", *Appl. Phys. Lett.*, vol. 89, iss. 13, pp. 133512-1–133512-3, 2006.

- [92] L. F. Edge, D. G. Schlom, P. Sivasubramani, R. M. Wallace, B. Holländer, and J. Schubert, "Electrical characterization of amorphous lanthanum aluminate thin films grown by molecularbeam deposition on silicon", *Appl. Phys. Lett.*, vol. 88, iss. 11, pp. 112907-1–112907-3, 2006.

- [93] M. Suzuki, T. Yamaguchi, N. Fukushima, and M. Koyama, "LaAlO<sub>3</sub> gate dielectric with ultrathin equivalent oxide thickness and ultralow leakage current directly deposited on Si substrate", *J. Appl. Phys.*, vol. 103, iss. 3, pp. 034118-1–034118-5, 2008.

- [94] X. B. Lu, Z. G. Liu, Y. P. Wang, Y. Yang, X. P. Wang, H. W. Zhou, and B. Y. Nguyen, "Structure and dielectric properties of amorphous LaAlO<sub>3</sub> and LaAlO<sub>x</sub>N<sub>y</sub> films as alternative gate dielectric materials", *J. Appl. Phys.*, vol. 94, iss. 2, pp. 1229–1234, 2003.

- [95] M. Suzuki, M. Tomita, T. Yamaguchi, and N. Fukushima, "Ultrathin (EOT = 3Å) and low leakage dielectrics of La-aluminate directly on Si substrate fabricated by high temperature deposition", in *Proc. IEEE IEDM Tech. Dig.*, Washington, USA, 2005, pp. 433–436.

- [96] A. Laha, A. Fissel, E. Bugiel, H. J. Osten, "Crystalline ternary rare earth oxide with capacitance equivalent thickness below 1 nm for high-k application", *Appl. Phys. Lett.*, vol. 88, iss. 17, pp. 172107-1–172107-3, 2006.

- [97] T.-M. Pan, C.-S. Liao, H.-H. Hsu, C.-L. Chen, J.-D. Lee, and K.-T. Wang, "Excellent frequency dispersion of thin gadolinium oxide high-k gate dielectrics", *Appl. Phys. Lett.*, vol. 87, iss. 26, pp. 262908-1–262908-3, 2005.

- [98] A. N. Nazarov *et al.*, "Charge trapping in ultrathin Gd<sub>2</sub>O<sub>3</sub> high-k dielectric", *Microelectron. Eng.*, vol. 84, iss. 9–10, pp. 1968–1971, 2007.

**Ivona Z. Mitrovic** received the Ph.D. degree in electronic engineering from the University of Liverpool, UK, in 2007, the M.Sc. degree in materials science from the University of Belgrade in 2002, and Dipl.-Ing. degree in microelectronics from the Faculty of Electronic Engineering, University of Nis, Serbia, Yugoslavia, in 1997. She

took part in a research project concerning BaTiO<sub>3</sub> ceramics (1997–2001), worked as a Research Assistant (2001–2007) and a Research Associate at the University of Liverpool (2000–2009). Since June 2009, she is a Lecturer in the Solid State Electronics Research Group, Department of Electrical Engineering and Electronics, University of Liverpool. Her research interests span materials for beyond 22 nm technological node targeting energy harvesting products for medical, automotive and aerospace applications, as well as emerging technologies for energy conversion and storage.

e-mail: ivona@liverpool.ac.uk

Department of Electrical Engineering and Electronics University of Liverpool

Brownlow Hill, Liverpool L69 3GJ, United Kingdom

**Stephen Hall** has been Head of the Department of Electrical Engineering and Electronics at the University of Liverpool, UK, from 2001 to the present date. He has interests spanning materials characterization, device physics and innovative device design and gate level circuits. He has over 200 conference and journal pa-

pers in the area of silicon technology, devices and circuits. These include novel measurements and contributions to the understanding of MOS related interfaces and materials quality. He has successfully designed and built novel MOS and bipolar devices in silicon for about 20 years. More recently, his work encompasses gate level circuits relating to low voltage/low power SOI, micro-power and biologically inspired concepts. He was Technical Programme Chair of ESSDERC 2008, and currently sits on the Steering Committee of ESSDERC/ESSCIRC and INFOS, for which he was vice-Chair in 2009 and is a member of the Steering Committee from 2009.

e-mail: s.hall@liverpool.ac.uk

Department of Electrical Engineering and Electronics University of Liverpool

Brownlow Hill, Liverpool L69 3GJ, United Kingdom