# Power electronic transformer based on cascaded H-bridge converter

# M. MORAWIEC\* and A. LEWICKI

Gdansk University of Technology, 11/12 Narutowicza St., 80-169 Gdańsk

**Abstract.** In this paper the control strategy of power electronic transformer (PET) is proposed. The analyzed structure of PET uses two seven-level cascaded H-bridge (CHB) rectifiers. The electrical power of PET is transferred between DC-links of CHB converters using dual-active-bridges (DABs) and low voltage high frequency transformers. The roposed solution allows for controlling the active and reactive power with a low level of harmonic distortions. The DC-link voltages and the load of the utilized H-bridges are controlled using appropriate modulation strategy. The theoretical issues are confirmed by simulation and experimental results.

Key words: power electronic transformer, cascaded H-bridge, rectifier control, control system.

### 1. Introduction

Power-electronic converters are widely used in smart grid applications. They can be used in active filter applications for total harmonic distortion (THD) improvement and reactive power compensation, in energy storage systems, as well as for the integration of renewable generation systems [1, 2]. Usually, electrical energy is converted using medium-voltage (MV) converters. medium voltage converters can be based on current source inverter topology (CSI) with thyristors as switching devices [19–20]. However, the CSI drawbacks (the fact that current THD is approximately 10% or higher and the resonance problems) make voltage-source inverters an interesting solution for MV applications.

The MV converters can be based on two-level voltage source inverter (VSI) structure with high-blocking voltage IGBTs. This type of converters usually works with low switching frequency due to relatively high energy losses [3–5].

In smart grid applications, due to current THD, it is recommended to use the power-electronic converters with relatively high switching frequencies. This assumption determines the use of low-voltage transistors in the converter topology. Multilevel (ML) VSI solutions meet that requirement in MV applications [3, 6, 7, 21]. The output voltage of ML inverter is higher than the blocking voltage of transistors. Additionally, the low voltage IGBTs are characterized by higher switching frequencies and lower saturation voltage as compared with high-blocking voltage transistors. The shape of the output voltage of ML inverter is close to sinusoidal, and the voltage and current distortions are low.

The most popular structures of ML converters are diodeclamped, capacitor clamped and cascaded H-bridge (CHB)

Bull. Pol. Ac.: Tech. 65(5) 2017

Manuscript submitted 2017-02-28, revised 2017-05-31, initially accepted for publication 2017-07-24, published in October 2017.

inverters [6]. Among all types of inverters, cascaded H-bridge converters are the most interesting [7]. The main advantage of the CHB converter is its modular structure. Such converters are constructed using single cells with H-bridges and a capacitor. The converter output voltage is the sum of output voltages generated by the H-bridges. Increasing the level of inverter output voltage or increasing the amplitude of output voltage can be done easily by adding more cells to the converter structure [8]. The structure of the control system applied in CHB inverter can be the same for any number of H-bridges and levels of output voltage. The CHB converters are popular especially in renewable generation systems [9], as well as in energy storage systems [10] and STATCOM applications [11].

Each cell of a CHB converter includes an single-phase inverter, a capacitive DC-link and a rectifier. The voltage sources connected to the cells have to be independent or isolated [7, 12]. The galvanic isolation can be realized using grid-connected single-phase or multi-phase transformers [7] or using isolated DC-DC converters in CHB converter topology [13]. The application of DC-DC converters with high- or medium- frequency transformers makes the inverter cheaper and smaller.

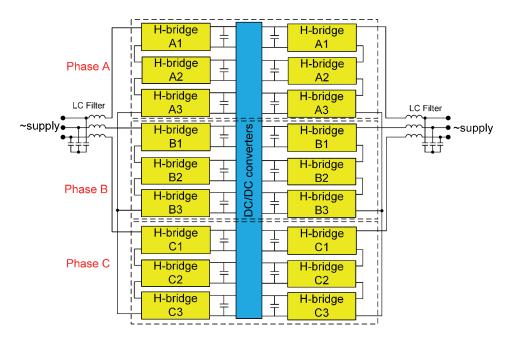

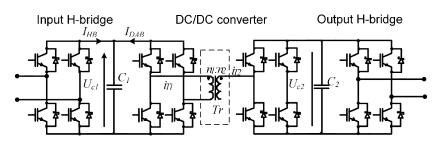

This paper concentrates on the structure and the control system of a power electronic transformer which is based on double CHB inverters. Such a PET configuration is presented in Fig. 1. The structure of power electronic transformer consists of two seven-level CHB converters, and the single cell of PET is shown in Fig. 2. The DABs with MF transformers transfer the energy between DC-link circuits. The presented solution reduces the size and cost of overall converter structures. The main task of the control algorithms for single CHB inverter is to generate the output voltage correctly and to maintain uniform voltage distribution on the DC-link capacitors. While the output voltage is generated, the DC-link voltages of the CHB converter vary depending on the CHB output voltage and current. The DC-link voltages can be equalized by sharing the generated output voltage between the H-bridges [14], by modifying their modulation indexes [15] or using fuzzy logic control loop [11].

<sup>\*</sup>e-mail: marcin.morawiec@edu.pg.gda.pl

Fig. 1. The structure of a power electronic transformer with 7-level CHB converter

Fig. 2. The structure of a single cell of PET

The uniform DC-link voltage distribution can also be maintained using separate controllers for each of the H-bridges of grid-connected CHB inverter [16].

The proposed control system was tested both in simulation and experimental studies. The experimental test was carried out on 600 kVA PET model. The PET with proposed control strategy was used to energy transfer between two 3.3 kV grids.

# 2. The PET control system and strategy

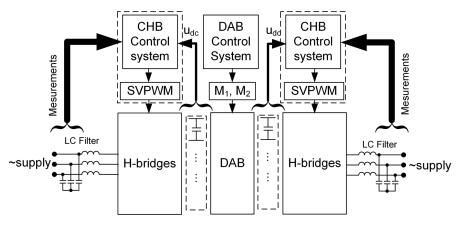

The main purpose of PET is to transfer the electrical energy between two grids. The reactive power of PET should be equal to zero. Because of the nominal voltage of capacitors, all the DC-link voltage should be the same. The PET control system scheme is presented in Fig. 3.

Fig. 3. The PET control system

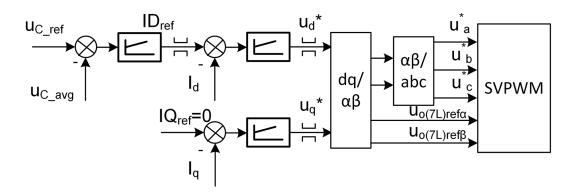

Fig. 4. The control system of multilevel rectifier

Proposed control structure of PET is based on two control systems:

- rectifier control system used to control active and reactive power of PET converters (Fig. 4),

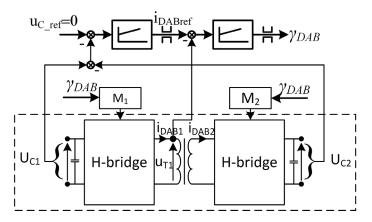

- DAB control system used to control the voltages on both capacitor of a single PET cell and to control the DAB current (Fig. 5).

The control system of the PET rectifiers should maintain a proper voltage value on DC-link capacitors. Since there are nine DC-link capacitors with different voltages in any of CHB rectifiers, the average voltage should be taken into consideration.

Fig. 5. The DAB control system

The space-vector pulse width modulation (SV-PWM) is used to generate the output voltage and to control the voltages on all DC-link capacitors (presented in Section 3)

The average values of the DC-link voltages can be calculated as:

$$U_{C(avgA)} = \frac{1}{3} \Big( U_{C(a1)} + U_{C(a2)} + U_{C(a3)} \Big), \tag{1}$$

$$U_{C(avgB)} = \frac{1}{3} \left( U_{C(b1)} + U_{C(b2)} + U_{C(b3)} \right), \tag{2}$$

$$U_{C(avgC)} = \frac{1}{3} \Big( U_{C(c1)} + U_{C(c2)} + U_{C(c3)} \Big), \tag{3}$$

where:

$U_{C(a1...3)}$  – DC-link voltages of phase a;  $U_{C(b1...3)}$  – DC-link voltages of phase b;  $U_{C(c1...3)}$  – DC-link voltages of phase c;  $U_{C(avgA)}$ ,  $U_{C(avgB)}$ ,  $U_{C(avgC)}$  – average DC-link voltages in a, b and c phases.

The average value of all DC-link voltages can be determined as:

$$U_{C(avg)} = \frac{1}{3} \left( u_{C(avgA)} + u_{C(avgB)} + u_{C(avgC)} \right). \tag{4}$$

The utilized control method of PET rectifier is based on well-known control system with classical PI controllers, realized in coordinate system oriented to the position of grid voltage vector (Fig. 4) [3, 7, 12]. In the proposed solution, the reference voltage vector, calculated by the rectifier control system, is additionally converted to three-phase system using inverse Clarke transformation. These phase voltages are utilized in SV-PWM modulation algorithm, presented in Section 3.

The simulation and experimental tests were done using the control system shown in Fig. 4, where the  $u_{C\_ref}$  is the reference average voltage of all DC-link capacitors.

In the proposed control system for PET, the active power of VSIs and the DABs are controlled independently, without exchanging information on the control processes. The DAB control system has been designed to maintain the same voltages on both capacitors in a single CHB cell (the difference between these voltages should be equal to zero, see Fig. 5).

The power transmitted by the MF transformer is controlled by the mutual phase shifting of two voltages: on primary and secondary transformer windings [17, 18]. The direction of trans-

Heruntergeladen am | 31.10.17 09:50

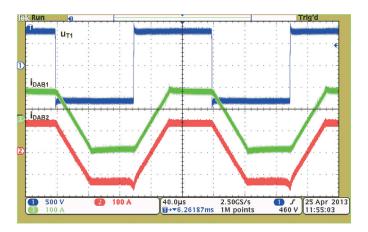

mitted active power depends on which of capacitor voltages is higher. The DAB currents  $i_{DAB1}$ ,  $i_{DAB2}$  and voltage  $u_{T1}$  on primary transformer winding shown in Fig. 6.

## 3. SVPWM strategy for CHB inverter

Each of H-bridges can be in active or bypass state. The H-bridges in active state generate positive or negative output voltage  $(0 < \gamma \le 1 \text{ or } -1 \le \gamma < 0)$ , while the output voltage of H-bridges in bypass state is equal to zero  $(\gamma = 0)$ . The voltage components of the seven-level CHB inverter (with three Hbridges connected in series in any of phase) can be calculated as:

$$u_{o\alpha(7L)} = \sum_{j=1}^{3} u_{o\alpha}^{j}, \quad u_{o\beta(7L)} = \sum_{j=1}^{3} u_{o\beta}^{j},$$

(5)

where:  $u_{o\alpha(7L)}$ ,  $u_{o\beta(7L)}$  are the components of the output voltage vector of the seven level converter in stationary orthogonal coordinate system  $\alpha\beta$ .

The output voltage vector  $\mathbf{u}_{o}$  is generated by three H-bridges (one H-bridge in any of inverter phases). Its components can be calculated as:

$$u_{oa} = u_{a(a)}^{x} + u_{a(b)}^{y} + u_{a(c)}^{z},$$

$$u_{o\beta} = u_{\beta(a)}^{x} + u_{\beta(b)}^{y} + u_{\beta(c)}^{z},$$

(6)

where x, y, z denote the H-bridge number  $(x, y, z = 1 \dots 3)$  in any of CHB phases, subscripts (a), (b), (c) denote CHB inverter phase.

The components of the output voltage vectors, generated in any of H-bridges, can be calculated as:

$$\begin{split} u_{\alpha(a)} &= \gamma_{(\alpha)} \cdot \sqrt{\frac{2}{3}} \cdot U_{C_{(a)}}, \\ u_{\beta(a)} &= 0, \\ u_{\alpha(b)} &= \gamma_{(b)} \cdot \sqrt{\frac{2}{3}} \cdot U_{C_{(b)}} \cdot \cos\left(\frac{2\pi}{3}\right), \\ u_{\beta(b)} &= \gamma_{(b)} \cdot \sqrt{\frac{2}{3}} \cdot U_{C_{(b)}} \cdot \sin\left(\frac{2\pi}{3}\right), \\ u_{\alpha(c)} &= \gamma_{(c)} \cdot \sqrt{\frac{2}{3}} \cdot U_{C_{(c)}} \cdot \cos\left(\frac{4\pi}{3}\right), \\ u_{\beta(c)} &= \gamma_{(c)} \cdot \sqrt{\frac{2}{3}} \cdot U_{C_{(c)}} \cdot \sin\left(\frac{4\pi}{3}\right), \end{split}$$

where:  $\gamma_{(a),\,(b),\,(c)}$  – duty cycles of H-bridge transistors in the phases: (a), (b) and (c), respectively,  $U_{C(a),\,(b),\,(c)}$  – DC-link voltages of H-bridges in these phases.

While the converter output voltage is higher than the DC-link voltages, some of the H-bridges must be in active states with

Fig. 6. The DAB currents  $i_{DAB1}$ ,  $i_{DAB2}$  and voltage  $u_{T1}$

duty cycles equal to  $\pm 1$ . These H-bridge transistors will not be switched during a single pulse period. The others will be in passive state, or their duty cycles will be in the range  $-1 < \gamma < 1$ .

If an H-bridge is in active state with the duty cycle equal to 1 or -1 the active power charges or discharges the DC-link capacitor for the whole pulse period. The selection of H-bridges used to generate the inverter output voltage depends on the direction of the instantaneous power and the DC-link voltages. If the following condition is fulfilled, the H-bridges with the lowest DC-link voltages will be used before the others:

$$i_{(p)} \cdot u_{(p)}^* > 0,$$

(8)

where:  $i_{(p)}$  is the "p" phase current of the CHB inverter (p = a, b or c),  $u^*_{(p)}$  is the reference phase voltage determined using the reverse Clarke transformation and the reference output voltage vector from the control system.

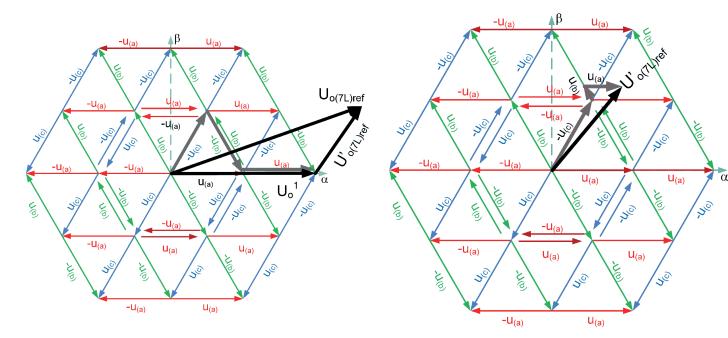

Otherwise, the H-bridges with the highest DC-link voltages will be used first. That is why the DC-links with the lowest voltages are charged while the DC-links with the highest voltages are discharged for the entire pulse period. The output voltage vector  $U_o^1$  generated in the three H-bridges (one H-bridge in any of inverter phases, chosen in a manner described above) with the duty cycles equal to  $\pm 1$ , as shown in Fig. 7. The next three H-bridges, chosen in the same manner, are utilized to generate the new reference voltage vector with coordinates (Fig. 7):

$$U'_{o(7L)ref\alpha} = U_{o(7L)ref\alpha} - U_{o\alpha}^{l}$$

$$U'_{o(7L)ref\beta} = U_{o(7L)ref\beta} - U_{o\beta}^{l}.$$

(9)

Where:  $U_{o(7L)ref}$  is the reference output voltage vector determined in PET control system,  $U'_{o(7L)ref}$  is the new reference voltage vector for the SV-PWM algorithm,  $U_o^1$  is the output voltage vector generated in three H-bridges.

If the maximum value output voltage generated by next three H-bridges is below the amplitude of the new reference voltage  $U_{o(7L)ref}$ , the duty cycles of these H-bridges are also

Fig. 7. The reference output voltage vector  $\mathbf{U}_{\mathrm{o}(7\mathrm{L})\mathrm{ref}}$  of the PET and the inverter output voltage vector  $U_{\mathrm{o}}^{1}$  generated in three H-Bridges with duty cycles  $\gamma_{(a)}=1$ ,  $\gamma_{(b)}=-1$ ,  $\gamma_{(c)}=-1$

Fig. 8. The new reference output voltage vector  $U'_{o(7L)ref}$  of the PET generated in three H-Bridges with duty cycles:  $0 < \gamma_{(a)} < 1$ ,  $0 < \gamma_{(b)} < 1$ ,  $\gamma_{(c)} = -1$

equal to  $\pm 1$ ; otherwise, some of duty cycles can be in the range  $-1 < \gamma < 1$ . In this case, the new reference output voltage can be generated as shown in Fig. 8.

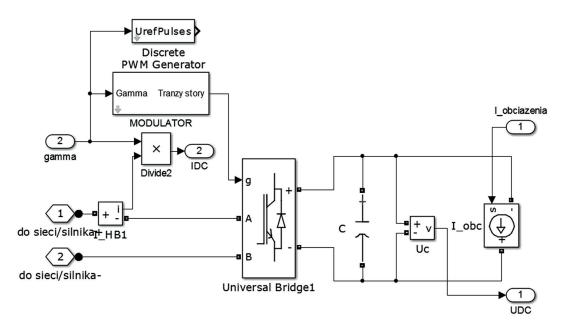

elements (over 100 IGBTs). The simulation model of the DAB system is presented in Fig. 9.

# 4. The Matlab-Simulink model of CHB converter

$$U_{HB} = \gamma \cdot U_C, \tag{10}$$

(11)

Simulation tests of PET with two seven-level CHB inverters (eighteen H-bridges), nine DABs and nine MF transformers are time-consuming, especially due to the high number of switching

$U_{HB}$  – H-bridge output voltage,  $U_C$  – DC-link voltage,  $I_{HB}$  – H-bridge current, I – grid current,  $\gamma$  – duty cycle of H-bridge transistors:

$I_{HR} = \gamma \cdot I$ ,

Fig. 9. Simulink model with IGBT with diodes; universal bridge

$$\gamma = \frac{U_o}{U_C},\tag{12}$$

where:  $U_o$  – the output voltage of a single H-bridge.

The duty cycle  $\gamma$  can be positive or negative, depending on the reference voltage sign. The only limitation is:

$$|\gamma| \le 1. \tag{13}$$

The main task of DAB converter is to maintain the same voltages on both DC-link capacitors. The adopted simulation model of DAB is based on a simplification: the energy delivered to the capacitor by the H-bridge is transferred to the secondary side of DAB transformer.

#### 5. Simulation results

The proposed control system was tested in the numerical Matlab-Simulink simulation. The grid voltage is 3.3 kV and the nominal current of PET is about 100 A. The nominal active power is 600 kVA. Each of the H-bridges is equipped with 1 mF capacitors.

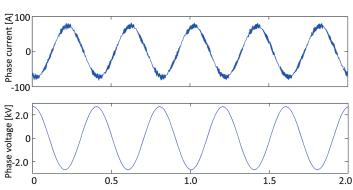

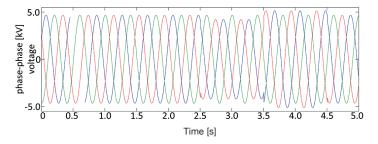

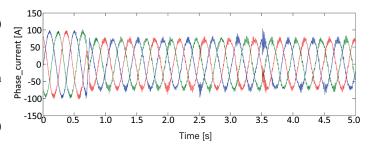

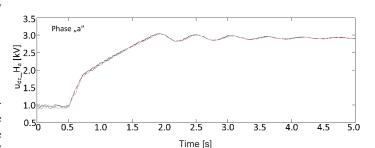

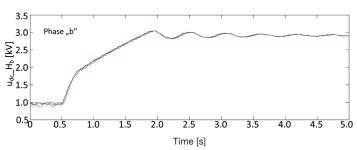

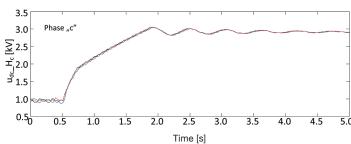

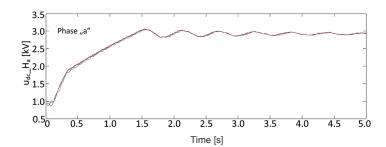

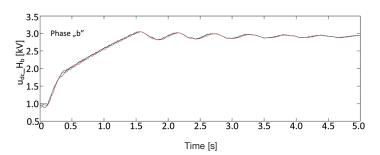

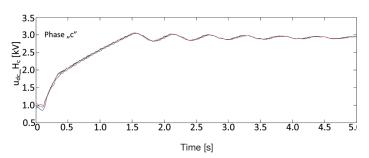

The phase current and voltage waveforms are shown in Fig. 10. The reactive power is equal to zero. Fig. 11 shows the phase to phase voltage and in Fig. 12, phase current during change of DC-link voltages up to 2.9 kV is shown. The DC-link voltages waveforms are presented in Fig. 13. The reference DC-link voltage is initially set to 1.1 kV, and increased to 2.9 kV

Fig. 10. The supply phase current and voltage in steady state

Fig. 11. The phase current and the phase to phase voltage. After about  $0.5~{\rm s}$  the capacitors voltage is changed to  $2.9~{\rm kV}$

Fig. 12. The phase current and the phase to phase voltage. After about 0.5 s the capacitors voltage is changed to 2.9 kV

Fig. 13. After 0 s the H-bridge capacitors voltage is stabilized to 1150 V, after 0.1 s the cascaded H-bridge rectifier capacitor voltage is turned on about 2900 V for phases a, b, c

after 0.1 s. For this case the AC grid phase "a" voltage was changed from 2.5 s to 0.8  $U_n$  and from 3.5 s to 1.2  $U_n$  from 4.5 s to nominal voltage  $U_n$ . This unbalanced AC grid voltage test (20%  $U_n$ ) shows that it does not directly affect stability of the whole PET system. Simulated changes of the AC grid voltage are for 1 s. The DC-link voltages remain on similar level for the three phases.

Small changes (additional oscillation time) of the DC-link voltages are visible in Fig. 14 during the test of AC-filter pa-

Fig. 14. After 0 s the H-bridge capacitor voltage is stabilized to 1150 V, after 0.1 s the cascaded H-bridge rectifier capacitor voltage is turned on about 2900 V for phases: a, b, c. The filter inductance was  $1.2 L_n$

rameter changes. For this case the inductance of the filter was changed about 20% in the simulation model (but not in the rectifier control system). The higher value of filter inductance affects PET in slower dynamic states. However, it has positive influence on phase current harmonics limitation. Therefore the filter parameters should be chosen so as to avoid the resonance problem and to provide the adequate performance and small size of the PET system.

## 6. Experimental results

Bull. Pol. Ac.: Tech. 65(5) 2017

The experimental tests were carried out on PET with two seven-level CHB inverters and nine DABs. The PET parameters were as follows: switching frequencies: DABs – 7 kHz, CHB inverters – 3.33 kHz, the nominal PET power – 600 kVA, nominal voltage – 3.3 kV, nominal phase current – 100 A, the DC-link reference voltage – 1 kV, the nominal blocking voltage of utilized IGBTs – 1.7 kV. The PET system parameters are presented in Table 1.

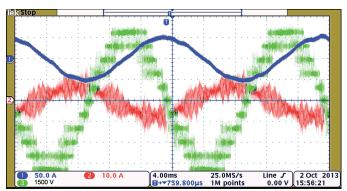

The waveforms of CHB inverter phase current (channel 1), the capacitor current of output filter (channel 2) and the output

Table 1 Nominal Parameters of Power electronic transformer

| Quantity                             | Values  |

|--------------------------------------|---------|

| Nominal Power                        | 600 kVA |

| Nominal phase current I <sub>n</sub> | 100 A   |

| Nominal phase voltage U <sub>n</sub> | 3.3 kV  |

| DAB nominal power                    | 70 kVA  |

| DAB nominal voltage                  | 1 kV    |

| DC-link capacitors voltage           | 1 kV    |

| DAB switching frequency              | 7 kHz   |

| Input and output rectifier frequency | 3.3 kHz |

| DC-link capacitors                   | 2.2 mF  |

| Filter inductance $L_f$              | 3 mH    |

| Filter resistance R <sub>f</sub>     | 0.1 Ω   |

| Filter capacitance C <sub>f</sub>    | 10 μF   |

voltage of CHB inverter (channel 3) obtained during the transfer of 300 kW active power are presented in Fig. 15.

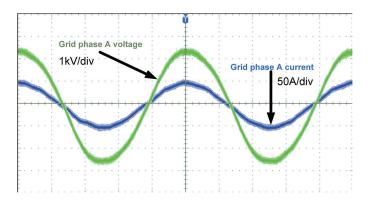

The PET phase current and grid phase voltage are presented in Fig. 16, which also shows that the unity power factor is obtained.

Fig. 15. The waveforms of CHB inverter phase current (channel 1), capacitor current of PET output filter (channel 2), and the output voltage of CHB inverter (channel 3). Transmitted active power – 300 kW

Fig. 16. The PET phase current and grid phase voltage

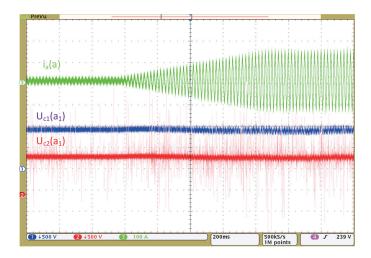

Fig. 17. The phase "a" current  $(i_{(a)})$  and the capacitor voltages of dual active bridge:  $U_{c1}$  – the capacitor voltage on the CHB rectifier side,  $U_{c2}$  – the capacitor voltage on the CHB inverter side (marks according to Fig. 6) during change of the active power from 10 kW to 550 kW. Scale: 100 A/div, 500 V/div, 200 ms/div

Phase "a" current and the input and output DAB voltages  $U_{c1}$  and  $U_{c2}$  during the change of the active power from 10 to 550 kW are presented in Fig. 17. The capacitors voltage is properly stabilized on referenced value. In dynamic states, the voltage changes are up to 50 V. The DC-link voltages (including their variations) should be below blocking voltages of transis-

tors or nominal voltages of passive circuit components. The actual values of DC-link voltages are taken into account during construction of the inverter output voltage vector in SVM algorithm. The output voltage is generated properly, the DC-link voltage unbalance notwithstanding.

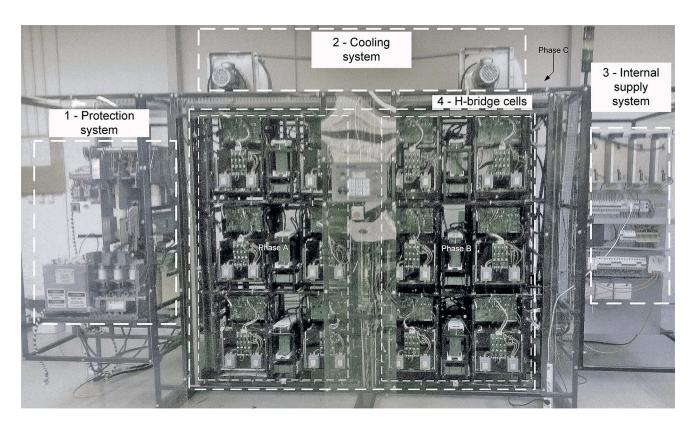

The experimental setup photo from laboratory is shown in Fig. 18.

### 7. Conclusions

The paper presents the control system, simulation and experimental results of the power electronic transformer. The PET system is based on two seven-level cascaded H-bridge converters. The control strategy for cascaded H-bridge converter and the space-vector pulse width modulation were analyzed. All theoretical assumptions are confirmed by the simulation and experimental results. The proposed control strategies for PET, cascaded H-bridge converters and dual-active bridges allow for stabilizing all the DC-link voltages and for controlling the transmitted power of PET. The input and output power factors of PET are equal to 1 and the PET efficiency is high. The efficiency and THD tests of proposed PET structure and control system gave the following results: the current THD is 3.4%, and the efficiency is 94.3%.

The control systems of the double CHB rectifier and all the DABs were not coupled and worked independently of each other. The proposed solution makes it possible to control the DC-link voltages in steady and transient states. The results of

Fig. 18. Experimental laboratory setup

the experimental test during change in DC-link voltages are shown in Fig. 17.

The PET system can be compared to traditional power transformer. Power transformer operates in a reliable manner and achieves high efficiency. It also has disadvantages, for example: large and bulky size, environmental impact of the transformer oil, breakdown voltage, the influence of the load fluctuation on the AC grid. The PET system is characterized by high efficiency (approx. 95%), smaller size, high frequency isolation transformers without oil and load fluctuation which does not affect AC grid side.

### REFERENCES

- [1] F. Gao, L. Zhang, Q. Zhou, M. Chen, T. Xu, and S. Hu, "State-of-charge balancing control strategy of battery energy storage system based on modular multilevel converter", *Proc. IEEE ECCE*, 2567–2574 (2014).

- [2] M.R. Islam, Y. Guo, M. Jafari, Z. Malekjamshidi, and J. Zhu, "A 43-level 33 kV 3-phase modular multilevel cascaded converter for direct grid integration of renewable generation systems", *Proc. Inn. Smart Grid Techn. IEEE ISGT Asia*, 594–599 (2014).

- [3] H. Abu-Rub, A. Lewicki, A. Iqbal, and J. Guzinski, "Medium voltage drives challenges and requirements", *IEEE International Symposium on Industrial Electronics*, 1372–1377 (2010).

- [4] D. Vinnikov, J. Laugis, R. Strzelecki, and M. Egorov, "6.5 kV IGBT switch realization possibilities and their feasibility study for high-power applications", 6th International Conference on Electrical Engineering, Cairo (2008).

- [5] D. Vinnikow, "High-voltage switch realization possibilities for the 3.0 kV dc fed voltage converters", 5th Int. Conf. Elect. Electron. Eng., Bursa (2007).

- [6] J. Rodríguez, J.Sh. Lai, and F. Zheng Peng, "Multilevel inverters: A survey of topologies, controls, and applications", *IEEE Trans. on Ind. Electronics* 49 (4), (2002).

- [7] M. Malinowski, K. Gopakumar, J. Rodriguez, and M.A. Pérez, "A survey on cascaded multilevel inverters", *IEEE Trans. Ind. Electron.* 57 (7), 2197–2206, (2010).

- [8] M.R. Islam, Y. Guo, and J. Zhu, "A high-frequency link multi-level cascaded medium-voltage converter for direct grid integration of renewable energy systems", *IEEE Trans. Power Electron.* 29 (8), 4167–4182 (2014).

- [9] C. Townsend, Y. Yu, G. Konstantinou, and V. Agelidis, "Cascaded H-bridge multi-level PV topology for alleviation of perphase power imbalances and reduction of second harmonic voltage ripple", *IEEE Trans. Power Electron.*, 1–1 (2015).

- [10] C. Liu et al., "Reliable transformerless battery energy storage systems based on cascade dual-boost/buck converters", *IET Power Electron.* 8 (9), 1681–1689 (2015).

- [11] G. Farivar, B. Hredzak, and V.G. Agelidis, "Reduced-capacitance thin-film H-bridge multilevel STATCOM control utilizing an analytic filtering scheme", *IEEE Trans. Ind. Electron.* 62 (10), 6457–6468 (2015).

- [12] J. Rodriguez, S. Bernet, B. Wu, J.O. Pontt, and S. Kouro, "Multi-level voltage-source-converter topologies for industrial medium-voltage drives", *IEEE Trans. Ind. Electron.* 54 (6), 2930–2945 (2007).

- [13] A. Goodman, A. Watson, A. Dey, J. Clare, P. Wheeler, and Y. Zushi, "DC side ripple cancellation in a cascaded multi-level topology for automotive applications", *Proc. IEEE ECCE*, 5916–5922 (2014).

- [14] A. Marzoughi and H. Imaneini, "Optimal selective harmonic elimination for cascaded H-bridge-based multilevel rectifiers", *IET Power Electron.* 7 (2), 350–356 (2014).

- [15] Y. Sun, J. Zhao, and Z. Ji, "An improved CPS-PWM method for cascaded multilevel STATCOM under unequal losses", *Proc.* 39th Annu. Conf. IEEE IECON, 418–423 (2013).

- [16] J. Chavarria, D. Biel, F. Guinjoan, C. Meza, and J.J. Negroni, "Energy-balance control of PV cascaded multilevel grid-connected inverters under level-shifted and phase-shifted PWMs", *IEEE Trans. Ind. Electron.* 60 (1), 98–111 (2013).

- [17] Z. Zhang, H. Zhao, S. Fu, J. Shi, and X. He, "Voltage and power balance control strategy for three-phase modular cascaded solid stated transformer", 1475–1480 (2016).

- [18] W. Choi, K.-M. Rho, and B.-H. Cho, "Fundamental duty modulation of dual-active-bridge converter for wide-range operation", IEEE Trans. Power Electron. 31 (6), 4048–4064 (2016).

- [19] D. Xu, N.R. Zargari, B. Wu, J. Wiseman, B. Yuwen, and S. Rizzo, "A medium voltage AC drive with parallel current source inverters for high power applications", *IEEE 36th Power Elec*tronics Specialists Conference (2005).

- [20] B. Wu and M. Narimani, "PWM current source inverters", published online: 24 DEC 2016, DOI:10.1002/9781119156079.ch10

- [21] A. Lewicki, Z. Krzeminski, and H. Abu-Rub, "Space-vector pulsewidth modulation for three-level NPC converter with the neutral point voltage control", IEEE Transactions on Industrial Electronics 58 (11), 5076–5086 (2011).

Bull. Pol. Ac.: Tech. 65(5) 2017